# Using the Alfa-1 Simulated Processor for Educational Purposes

GABRIEL A. WAINER Carleton University and SERGIO DAICZ, LUIS F. DE SIMONI, and DEMIAN WASSERMANN Universidad de Buenos Aires

Alfa-1 is a simulated computer designed for computer organization courses. Alfa-1 and its accompanying toolkit allow students to acquire practical insights into developing hardware by extending existing components. The DEVS formalism is used to model individual components and to integrate them into a hierarchy that describes the detailed behavior of different levels of a computer's architecture. We introduce Alfa-1 and the toolkit, show how to extend existing components, and describe how to use Alfa-1 for educational purposes. We also explain how to assemble, link, and execute applications and how to test new extensions using the testing tools.

Categories and Subject Descriptors: C.0 [Computer Systems Organization - General]: Modeling of Computer Architecture; I.6.5 [Simulation and Modeling]: Model Development; K.3.1 [Computers and Education]: Computer Uses in Education

General Terms: Design

Additional Key Words and Phrases: DEVS formalism, modeling computer architectures, systems specification methodology

## 1. INTRODUCTION

Computer organization courses are usually based on the description and analysis of the behavior of digital computers. The complexity of these is so high that they are usually described in layers defining different levels of abstraction. These layered descriptions allow greater insight when analyzing a given subsystem. In general, the following levels are described:

- a) *digital circuits*: in general, this level is described using Boolean logic;

- b) *microprogramming*: microprogrammed or hardwired control units are described using block diagrams, FPGA logic, etc.;

- c) *instruction sets* are described using diagrams and algorithmic descriptions;

- d) *assembly language* can be expressed using algorithmic descriptions and finite state automata (representing the assembler syntax).

© 2001 ACM 1531-4278/01/0300-0111 \$5.00

This research was supported by USENIX and NSERC. Authors' addresses: G. A. Wainer, Department of Systems and Computer Engineering, Carleton University, 1125 Colonel By Drive, Ottawa, ON K1S 5B6, Canada; email: gwainer@sce.carleton.ca. URL: http://www.sce.carleton.ca/faculty/wainer.html; S. Daicz, L. F. De Simoni, D. Wassermann, Computer Science Department, Universidad de Buenos Aires, P.B. Pabellón I. Ciudad Universitaria (1428) Buenos Aires, Argentina. Permission to make digital/hard copy of part of this work for personal or classroom use is granted without fee provided that the copies are not made or distributed for profit or commercial advantage.

This organization emphasizes understanding the details of the subsystems, but the complex interlayer interactions are not addressed. The introduction of higher levels of abstraction (such as programming languages or operating systems) makes the pedagogical tasks even more difficult. Another consequence of this organizational structure is the difficulty of providing practical experience in every layer. In most cases, training is only provided at the level of the instruction set, resulting in courses that focus on the higher level of the hierarchy, and thus lose the details of the interlevel interactions. In general, these kinds of courses are based on the classic bibliography of the area (for instance, Hennessy and Patterson [1994]; Patterson [1995]; Stallings [1999]; Heuring and Jordan [1997]; and Tanenbaum [1999]), which present detailed behavioral descriptions of the underlying subsystems. These descriptions are essential in understanding the system concepts. Nevertheless, covering the details of each of the subsystems is not feasible.

Consequently, students do not gain an understanding of system behavior as a whole *nor* detailed knowledge of the subsystems. They may even finish with incomplete and erroneous views of how a computer works, which may affect their progress in more advanced courses in an area (e.g., operating systems, embedded systems, computer architectures, etc.). We decided to attack these problems using simulation tools. Our goal is to provide the students with means of designing hardware architectures. Full understanding of the behavior of the different layers and their interaction can be achieved, thanks to the ability to acquire practical experience with the intralayer and interlayer behavior. In the first stage of this project, we analyzed several tools that were built in order to implement computer architectures. We recognized three basic categories of architecture simulator tools:

- A. general-purpose tools

- B. specific-purpose tools

- C. hardware description languages

The results of this study were presented in Wainer et al. [2002]. In that work, we classified our educational needs as follows:

- I. *Levels of abstraction*: we need tools that allow the student to gain experience with the different layers described in a computer system. In particular, we need

- 1. the ability to describe the multiple abstraction levels studied in computer organization courses; and

- 2. the capacity to define different components using a unique approach.

- II. *Pedagogical value*: we need tools that can be used easily by students taking computer organization courses. In particular, we require

- 1. the possible use by students in the early stages of their careers of new tools or programming languages that can be programmed without extra effort in areas that are out of the scope of computer organization courses;

- 2. a fast learning curve, due to the lack of time in one-term courses; and

- 3. resources available in the public domain.

# III. Modifiable models representing the architecture components, including

1. the ability to extend the architecture to include new components;

- 2. the ability to modify existing architectures, providing students with the opportunity to experience different configurations; and

- 3. ease in testing changes in the architecture.

IV. Study of advanced architectural facilities, including

- 1. the ability to reproduce existing architectures; and

- 2. the capacity to define state-of-the-art architectures.

We analyzed several existing tools according to these needs and classified their advantages in each of these categories. We included different examples of general- purpose tools, which can be applied to build any kind of processor by defining an instruction set, the computer organization, and its components. For instance, SimpleScalar [Burger and Austin 1997] allows different architectures to be defined using basic building blocks that can be used to model advanced architectural aspects. HASE (Hierarchical Architecture design and Simulation Environment) allows users to rapidly develop and explore computer architectures with multiple abstraction levels [Coe et al. 1996]. SimOS is a general-purpose tool [Rosenblum et al. 1997] that permits different architectural details to be defined by providing different CPU models (including descriptions of the architecture and components: caches, multiprocessor memory buses, disk drives, etc.). A large number of general-purpose tools are devoted to model multiprocessor simulations. Some examples can be found in Ikodinovic et al. [1999]; Brewer et al. [1991]; Burns et al. [2000]; Bedichek [1995]; Shanmugan et al. [1992]; and Hein and Dal Cin [1998]. None of them meet our educational requirements; instead, they are best suited for higher-level courses to support lectures on computer architecture.

Another possibility is to describe the details of a given architecture using any of the existing *hardware description languages*. For instance, VHDL [Ghosh 2000] can be used for documentation, verification, and synthesis of large digital designs, using structural, dataflow, and behavioral methods. Verilog [Thomas and Moorby 1991] is easier to learn than VHDL, but lacks constructs to support system-level design (structural models are built from gate primitives and other modules). SDL [Mitschele-Thiel 2000] was developed as a description language for reactive systems, and uses extended finite states presented in a graphical form.

Several of the existing tools were built for the *specific purpose* of emulating existing architectures. Some tools focus on the *Intel* 80x86. For instance, Augmint [Nguyen et al. 1996]; Virgo [Pearce 2000]; and Simx86 [Shealy et al. 1997] focus on the instruction set level and the assembly language level of 8086-based computers. Other environments are based on the *MIPS* architecture. MPS [Morsiani and Davoli 1999] defines RAM, ROM, the processor, disks, tapes, printer, and terminal. Spim [Hennessy and Patterson 1997] implements an assembler-extended instruction set for the MIPS, omitting some of the complex details. *Alpha* processor simulators are presented in Edmonson and Reilly [1998], enabling developers to analyze pipelining levels and instruction-level parallelism. THRsim11 [Anderson et al. 1999] emulates the *Motorola* 68HC11 microcontroller in its entirety, including memory, CPU registers, I/O ports, a timer, pulse accumulator registers, AD converter registers, and other standard features.

| Name/Category              |   |   | I |   | II |   |   | III |   |   | IV |   |

|----------------------------|---|---|---|---|----|---|---|-----|---|---|----|---|

|                            |   | 1 | 2 | 1 | 2  | 3 | 1 | 2   | 3 | 1 | 2  | 3 |

| Alpha Emulator             | В | - | - | - | -  | - | - | -   |   | + | +  | - |

| Alfa-0                     | В | - | - | + | +  |   | - | -   |   | - | -  |   |

| CASLE                      | В | - | - | + | +  |   |   | -   |   | - | -  |   |

| CHIP                       | В | - | - | + | +  |   | - | -   |   | - | -  |   |

| CPU-Sim                    | В | - | - | + | +  |   | - | -   |   | - | -  |   |

| ESCAPE/DLX                 | В | + | - | + | +  |   | - | +   | - | - | +  |   |

| HASE                       | Α | + |   | - | -  |   | + | +   | + | + | +  | - |

| Limes                      | В | - | - | - | -  |   | - | -   |   | - | +  | - |

| MPS                        | В | - | - | + | +  |   | - | -   |   | + | -  |   |

| PROTEUS                    | В | - | - | - | -  |   | - | -   |   | - | +  | - |

| PROVIR                     | В | - | - | + | +  |   | - | -   |   | - | -  |   |

| SDL                        | С | + | + | - | -  | - | + | +   | + | + | +  |   |

| SimOS                      | Α |   | - | - | -  |   | + | +   | + | + | +  | - |

| SimpleScalar               | Α | - | - | - | -  |   | + | +   | + | + | +  | - |

| SimX86                     | В | - | - | + | +  |   | - | -   |   | + | -  |   |

| SPIM                       | В | - | - |   |    |   | - | -   |   | + |    |   |

| Verilog                    | С | + | + | - | -  | - | + | +   | + | + | +  |   |

| VHDL                       | С | + | + | - | -  | - | + | +   | + | + | +  |   |

| Virgo/SimX86               | В | - | - | + | +  |   | - | -   |   | + | -  |   |

| Z80/68HC11/Atari emulators | В | - | - | + | +  |   | - | -   |   | - | -  |   |

**Table I. Comparing Architecture Simulators**

Other authors emulated systems based on processors that nowadays are obsolete. El Hajj et al. [2000] presented a method for simulating the *Z80* processor using spreadsheets. Q-Emulator [Zidlicky et al. 2002] is a software emulator of the QL Sinclair PC, which interprets the Motorola *68008* instructions, redirecting input and output to a Mac or PC video, keyboard, mouse, disks, sound hardware, and serial ports. A similar approach was taken in PLM [Isacovich et al. 1999]. This work was devoted to providing an emulator for the *Atari* processor, enabling Atari programs to be run on Intel-based computers. The CHIP (Cornell Hypothetical Instructional Processor [Babaoglu et al. 1983]) emulates a *PDP-11* (including dynamic memory mapping, two modes of processor operation, and eight interrupt priority levels). PROVIR [Bevilacqua et al. 2000] is based on the *IBM 360* architecture (including an assembler, a debugger, and the kernel of an operating system).

In our study we found that the most adequate tools, in an educational sense, are specific-purpose tools that define a fictitious computer architecture and are tailored to educational needs. CASLE [Deitz and Adams 1994] is a Web-based computer using its own instruction set. The interface automatically produces an optimizing compiler, assembler, and architectural simulator using the specified architecture. Students can experiment with the effects of changing the number of registers, instruction latencies, optimizations, etc. Alfa-0 [Wainer et al. 2001] and the Rudimentary Computer [Pastor and Sánchez 1997] are two examples of very simple instruction set computers with educational purposes. These computers enable the representation of some

details of the datapath, microprogramming, and instruction set levels. They include a reduced number of registers and instructions in order to simplify the analysis of the problem. CPU-Sim [Skrien 1994] is a Java application that allows users to design simple processors at the microcode level and to execute programs written in machine language. It permits assembly language programs to be written and debugged, and allows analysis of the state of the machine. Finally, ESCAPE [Campenhout et al. 1998] is based on the DLX architecture [Hennessy and Patterson 1997]. The tool enables users to create their own instructions, to modify the numbers of registers, and the size of immediate operands, and so on.

The results of this survey are summarized in Table I. We show a set of different tools, their types, and classify their features according to the categories presented previously. The '+' sign represents a tool that fulfills our goals and the '-' sign represents a tool that does not meet our goals. Column IV.3 shows the tools that are especially tailored for studying multiprocessor architectures.

When we analyze Table I we can see that none of the tools (which, in fact, represent a sample of the different kinds of existing tools) suit our needs. Many tools are strong in a given category but weak in others. If we analyze category I, we can see that only a few tools are able to represent the multiple layers required. Nonetheless, they are weak from the pedagogical standpoint. Tools that are strong candidates from a pedagogical perspective are weak from some others: they are too simple, or do not permit the underlying organization to be modified. This pattern is repeated when we consider the modifiability of tools. The most interesting candidates are too complex in terms of learning. The best choice is the ESCAPE tool, based on the DLX architecture. Nevertheless, this tool implements a nonexistent processor, and each of the abstraction levels are represented using different formalisms, making it more difficult to accomplish a thorough study of the architecture.

We decided to build a new set of simulation tools that could meet all our goals. The tools can be used by anyone who has a basic knowledge of programming techniques; they are public domain, and have been built using public domain software. The tools were built to be fully understood by people who have taken an introductory course in computer programming. The hierarchical and discrete event nature of the problem made DEVS [Zeigler et al. 2000] a good choice to ease the development task. DEVS provides a system-theoretic framework for describing discrete event systems as a composite of submodels that can be simulated by abstract entities. As we will show, all of the levels usually described in computer organization courses can be developed using DEVS as the modeling framework. In DEVS theory, every existing model can be integrated into a hierarchy, allowing reuse of tested models (which we have done extensively in this project).

We started the project as a specific-purpose architecture based on a modern architecture (the SPARC processor). The model-oriented nature of DEVS resulted in a set of components that can be integrated to define existing architectures (at present, Intel and DSP model architectures are being developed). Hence, we have built a general-purpose toolkit that is specialized as a special-purpose tool.

DEVS enables a modeler to focus on the problem to be solved, as abstract simulators are in charge of execution. Behavioral (atomic) or structural (coupled) models can be

defined within a modeling hierarchy. A DEVS atomic model is described by

$M = \langle X, S, Y, d_{int}, d_{ext}, I, D \rangle$ X: input events set S: state set Y: output events set  $\mathbf{d}_{int}: S \rightarrow S$ , internal transition function  $\mathbf{d}_{ext}: QxX \rightarrow S$ , external transition function, with  $Q = \{(s,e)/s \in S, and e \in [0,D(s)]\}$ I:  $S \rightarrow Y$ , output function D:  $S \rightarrow R_0^+$  elapsed time function

Each model uses input/output ports in the interface (defined by the X and Y sets) to communicate with other models. When an input external event is received in an input port, it activates the external transition function, which produces a change of state. The new state has an associated lifetime, after which the internal transition function is activated (producing a new state change). The model can generate data to be transmitted through the output ports. The output function, which is in charge of this task, is activated before the execution of the internal transition function.

DEVS atomic models can be used to build coupled models. It was proven that DEVS coupled models are semantically equivalent to atomic models. Consequently, it is possible to build different semantically equivalent modeling hierarchies. A DEVS coupled model is defined by

$CM = \langle X, Y, D, \{M_i\}, \{I_i\}, \{Z_{ij}\} \rangle$ X: input events set Y: output events set D: index of components, and  $i \geq D$   $M_i$ : basic DEVS model  $I_i$ : influencees of model i, and  $P \in P_i$  $Z_{ij}: Y_i \to X_i$ , the i to j translation function

Each coupled model is composed of a set of basic models (atomic or coupled) connected through their input/output ports. Each component is identified by an index number. The influencees of a model are those receiving the outputs of the model. The translation function transforms the outputs of a model to the inputs of others. First, we create an index of influencees for each model (I<sub>i</sub>). We then define which outputs of model  $M_i$  are connected to inputs in model  $M_j$  by using the set of influencees. When two submodels have external simultaneous events, the *select* function prescribes which of them should be activated first.

There are different tools that implement the theoretical concepts defined by the DEVS formalism (DEVSJava, DevsSim++, DEVS-C++, JDEVS, DEVS-Scheme, etc.). We used the CD++ tool, which is public domain and fits our needs [Rodriguez and Wainer 1999; Wainer et al. 2001; Wainer and Troccoli 2001]. In this tool, atomic models are programmed in C++, enabling users with basic programming skills to develop

new models. Coupled models are defined using a built-in specification language, which represents the model coupling scheme. The detailed design and implementation results of this project are presented in Wainer et al. [2002].

In the following sections we explain how the tool can be used and modified. We also show how the tools were used in computer organization assignments and how to repeat this experience in a classroom. We organized the article according to the model's architecture and organization. Stallings [1999] states that the term computer *architecture* refers to those attributes of a system visible to a programmer, and that computer *organization* refers to the operational units and their interconnections. We start by describing the organizational level, focusing on the definition and modification of components. We then discuss the system architecture level, showing how a programmer can use the services provided by the computer (including examples of executable files). We subsequently present a set of tools devoted to improving testing, and an ongoing effort to building a GUI for the toolkit. Finally, we present a set of activities that can be carried out using the toolkit.

## 2. THE ORGANIZATION LEVEL

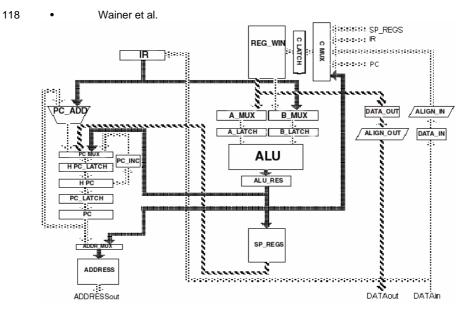

The Alfa-1 simulated computer is built as a set of interacting submodels representing the behavior of the architectural components. As we mentioned, Stallings [1999] defines computer organization as to the operational units and their interconnections that realize architectural specifications. Organizational attributes include those hardware details transparent to the programmer, such as control signals, interfaces between the computer and peripherals and the memory technology. The Alfa-1 processor organization is based in the specification of the integer unit of the SPARC processor [Sun 2001], and is shown in Figure 1. The processor includes 8 global registers (*RegBlock*).

The processor includes several special-purpose registers:

- 1. *PC*s: there are two program counters. PC contains the address of the next instruction, and nPC stores the address of the next PC. If the instruction is a conditional branch, nPC is assigned to PC, and nPC is updated with the jump address.

- 2. *CWP* (circular window pointer) is a specialized 5-bit register that marks the active window. Every time a new procedure starts, *CWP* is decremented.

- 3. PSR (processor status register) stores the program status.

- 4. *Y* is used by the product and division operations. Multiplication uses 32-bit operands, producing 64-bit results. The 32 most significant bits are stored in Y, and the remaining bits are stored in the ALU-RES register. The integer division operation takes a 64-bit dividend and a 32-bit divisor, producing a 32-bit result. The Y register stores the 32 most significant bits of the dividend. One ALU input register stores the least significant bits of this number, and the other, the divisor. The integer result is stored in the ALU-RES register and the remainder is stored in the Y register.

Fig. 1. Organization of the integer unit [Wainer et al. 2002].

- 5. *BASE* and *SIZE*: we used a flat memory addressing scheme. The BASE register points to the lowest address a program can access. SIZE stores the program size, which represents the maximum addressable memory unit.

- 6. *WIM* (window invalid mask) is a 32-bit register used to avoid overwriting a register window. When CWP is decremented (because a procedure was called), the WIM bit is verified for the new window. If it is active, an interrupt is raised and the service routine must store the window contents in memory. WIM usually marks the oldest window.

- 7. *TBR* (trap base register) points to the memory address storing the location of trap routines.

The processor was implemented using the CD++ tool. In a first stage, we specified the behavior of each component, analyzing inputs and outputs of the original circuits. These specifications allowed test cases to be derived (details of this phase can be found in Daicz et al. [1998]). Each subcomponent of the computer was then defined using DEVS as the specification formalism. Using these descriptions, each model was implemented in the CD++ toolkit. Each of the models can be reused in building different architectures. Each model has an associated experimental framework that allows the derived test cases to be executed (details of this phase can be found in De Simoni et al. [1998]). Thirty-five different circuits were defined as DEVS atomic or coupled models and were integrated into the architecture. Several of these models were defined as multicomponents based in digital logic. A set of Boolean gates was included, and these models enabled us to define some of the submodels at the digital logic level. Details about the existing models and their various implementations can be found in Wainer et al. [2002].

```

class AtomicState : public ModelState {

public:

enum State {

active,

passive

};

State st;

AtomicState(){};

virtual ~AtomicState(){};

AtomicState& operator=(AtomicState& thisState);

void copyState(BasicState *);

int getSize() const;

};

```

Fig. 2. The AtomicState class.

Finally, the main model was built as a coupled model connecting all the submodels defined previously. The CPU executes under the supervision of the control unit. It receives signals from the rest of the processors using 64 input bits (organized in 5 groups: the instruction register, the PSR, BUS\_BUSY\_IN, BUS\_DACK\_IN, and BUS\_ERR). Its outputs are sent using 70 lines organized in 59 groups. Some of them include read-ing/writing internal registers, activating lines for the ALU or multiplexers. In addition, connections with the PC, nPC, trap controller, and PSR registers are included. Finally, the data, address and control buses can be accessed. The control unit was defined using microprogramming concepts. Hence, by modifying the control unit, students can gain experience at the microprogramming level.

After running the individual tests for each of the components, we executed integration tests. Integration required combining all of the components and defining their interactions to represent the execution flow of the computer. Execution flow tasks are carried out by the control unit, which, in this case, was built as a DEVS model using several input/output ports representing the CU lines. According to the input received, it issues appropriate outputs by activating the different circuits that were defined previously (details can be found in De Simoni et al. [1998]). Finally, a thorough integration test was executed; the results of this phase are presented in Section 4.

The first step needed is to install the required tools. The instructions to do so can be found at

<<u>http://www.sce.carleton.ca/faculty/wainer/alfa-1.html</u>>.

After installing the tools successfully, different activities can be carried out. Many of them involve modifying or extending the existing components. To do so, atomic models may need to be changed, or new models may be added and integrated with existing coupled models. The following section is devoted to showing how to code new models or modify existing ones, following the guidelines presented in Wainer and Troccoli [2001]. We then show how to introduce new atomic and coupled models into the simulated computer, which may be carried out as a course assignment.

ACM Journal of Educational Resources for Computing, Vol. 1, No. 4, December 2001.

.

## 2.1. Defining New Models

In CD++, a new atomic model is created as a new class derived from the *Atomic* base class. The state of the model is composed by the variables that can be changed during a simulation cycle, which are defined in the *AtomicState* class in Figure 2.

When creating a new atomic model, a new class derived from atomic has to be created. *Atomic* is an abstract class that declares a model's API and defines some service functions the user can use to write the model. The *Atomic* class (Figure 3) provides a set of services and requires a set of functions to be redefined:

- 1. *holdIn(state, Time)* tells the simulator that the model will remain in the state *state* for a period *time*. It corresponds to the D(s) DEVS atomic function.

- 2. *passivate()* sets the next internal transition time to infinity. The model will only be activated again if an external event is received.

- 3. *sendOutput(Time, port, BasicMsgValue\*)* sends an output message through the port. The time should be set to the current time.

- 4. nextChange() returns the remaining time for the next internal transition.

- 5. *lastChange()* returns the time since the last state change.

- 6. *state()* returns the phase of the current model.

The new class should overload the following functions:

1. virtual Model & externalFunction( const ExternalMessage & ) is invoked when one external event arrives to a port. It corresponds to the  $\delta_{ext}$  function of the DEVS formalism.

```

class Atomic : public Model {

public:

virtual ~Atomic(); // Destructor

protected:

//User defined functions.

virtual Model &initFunction() = 0;

virtual Model &externalFunction( const ExternalMessage & );

virtual Model &internalFunction( const InternalMessage & ) = 0 ;

virtual Model &outputFunction( const CollectMessage & ) = 0 ;

virtual string className() const

//Kernel services

Time nextChange();

Time lastChange();

Model & holdIn( const AtomicState::State &, const Time & ) ;

Model &sendOutput(const Time &time, const Port & port , Value value)

Model &passivate();

Model &state( const AtomicState::State &s )

{ ((AtomicState *)getCurrentState())->st = s; return *this; }

}; // class Atomic

```

Fig. 3. The atomic class.

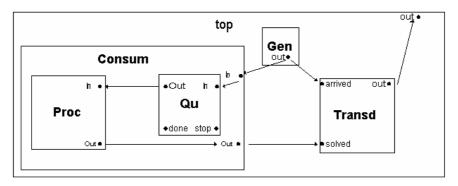

Fig. 4. A consumer/producer scheme [Zeigler et al. 2000].

- 2. virtual Model &internalFunction( const InternalMessage & ) corresponds to the  $\delta_{int}$  function of the DEVS formalism.

- 3. *virtual Model &initFunction()* is invoked by the simulator at the beginning of the simulation and after the model state has been initialized.

- 4. *virtual Model & outputFunction( const CollectMessage & )* is in charge of sending all of the output events of the model.

After each atomic model is defined, they can be combined into a multicomponent model. Coupled models are defined using a specification language especially defined for this purpose. The language was built following the formal definitions for DEVS coupled models (Figure 4). Optionally, configuration values for the atomic models can be included.

The [*top*] model always defines the coupled model at the top level. As shown in formal specifications presented in Section 1, four properties must be configured: components, output ports, input ports, and links between models.

The following syntax is used:

**Components:** model\_name1[@atomicclass1] [model\_name2[@atomicclass2] ... This sentence is used to list the components comprising the coupled model. A coupled model may include atomic models and/or other coupled models as components. If we include an atomic component, we must specify an instance and a class name. This allows a coupled model to use more than one instance of an atomic class. For coupled models, only the model name must be given. This model name must be defined as another group in the same file.

**out**: portname1 portname2 ... enumerates the output ports of the model. This clause is optional because a model may not have output ports.

**In**: portname1 portname2 ... enumerates the input ports. This clause is also optional because a coupled model is not required to have input ports.

**Link:** source\_port[@model] destination\_port[@model] ... describes the internal and external coupling scheme. The name of the model is optional. The model used by default is the coupled model currently being defined.

[top] components : Transd@Transducer Gen@Generator Consum Out : out Link : out@generator arrived@transducer Link : out@generator in@Consumer Link : out@generator in@Consumer Link : out@consumer solved@transducer Link : out@consumer solved@transducer Link : out@transducer out [Consum] components : Qu@Queue Proc@CPU in : in out : out Link : in in@qu Link : in in@qu Link : out@qu in@Proc Link : out@Proc done@qu Link : out@Proc out

Fig. 5. Example for the definition of a DEVS coupled model.

Figure 5 shows a sample of a coupled model representing a simple consumer/producer scheme. It consists of three models: a generator that creates data to be consumed, a consumer, and a transducer that measures the consumer speed. The consumer is a coupled model, composed of a processor and a queue to keep waiting jobs.

At the top level of this example, the *Generator* influences the *Transducer* and the *Consumer*. The *Consumer* also influences the *Transducer*, as well as the *Queue*. The *Processor* influences the *Consumer* and the *Queue* influences the *Processor*. Finally, the *Transducer* influences the top model. These interconnections define the influence sets for each of the components. The influencee sets are used to define the translation functions, which transfer data through the input/output ports in the models.

## 2.2. Modeling at the Organization Level: A Simple Look-Aside Component

The remainder of Section 2 shows simple examples of the educational activities that can be carried out at the organization level (the models developed here were built as assignments in a computer organization course). We show how a user can modify or change existing components, focusing on extending the simulator by adding components external to the processor.

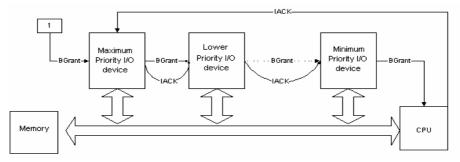

Look-aside components (usually input/output devices) are attached to one of the bus slots. In order to be able to add any new component, we must know the bus protocol used for Alfa-1. If we analyze the descriptions in Daicz et al. [1998], we can see that the bus uses the lines in Table II.

In each data transfer, we can identify an active and a passive component. All the active components are chained by a bus grant line (BGRANT), used to receive a signal from the component with next higher priority and to send a signal to the component with next lower priority (Figure 6). The active component must take over the bus. First, it requests to be the next one to use the bus. If the component requesting the bus receives a 1 over the BGRANT input line, this means that none of the components with higher priority need the bus. Then, it sends a 0 over the BGRANT output line, telling the components with lower priority that it is intending to use the bus. It must then wait until a 0 is received over the BUSY line, meaning that the bus is no longer being used.

| Pin Name      | In | Out | Description       |  |  |  |  |  |  |

|---------------|----|-----|-------------------|--|--|--|--|--|--|

| Data0-31      | Х  | X   | Data              |  |  |  |  |  |  |

| A0-31         | Х  | X   | Address           |  |  |  |  |  |  |

| Clock         | Х  | X   | Clock             |  |  |  |  |  |  |

| AS            | Х  | X   | Address Strobe    |  |  |  |  |  |  |

| RD <u>/WR</u> | Х  | X   | Read or Write     |  |  |  |  |  |  |

| DTACK         | Х  | X   | Data Acknowledge  |  |  |  |  |  |  |

| Err           | Х  | X   | Error             |  |  |  |  |  |  |

| RESET         | Х  | X   | Reset             |  |  |  |  |  |  |

| IRQ1-15       | Х  | X   | Interrupt Request |  |  |  |  |  |  |

| Busy          | Х  | X   | bus Busy          |  |  |  |  |  |  |

Table II. Alfa-1 Bus Lines

Fig. 6. Active components BGRANT chain [Wainer et al. 2002].

Finally, it will send a 1 over the BUSY line to let the other components know that the bus is being used.

After the bus is taken, the address to be accessed should be written to the address bus (A0-31). The access to memory involves two parameters. First, the active component chooses which 32-bit memory word will be used and sets the address on the address bus. The second parameter allows a 32-bit word to be split into four bytes (D0-7, D8-15, D16-23, D24-31) and it must be specified. The BSEL bits are used to choose the desired bytes: if the active component sets BSEL0, D0-7 will be addressed (BSEL1 corresponds to D8..15, etc.). If the active component requested a write operation (clearing RD/WR), the data to be written should be sent over the selected bytes of the data bus (D0-31). The active component will subsequently send a 1 over the AS line (letting the passive component know that everything is set), and will wait for the DTACK line to be set (which means that the request has been fulfilled). If the operation is a read, the data on the D31-0 lines is collected. The active component can start another operation (it still controls the bus) by setting BGRANT and clearing BUSY to release the bus.

The passive component (for instance the main memory) will use a different protocol. It will first receive a read or write request from the active component, represented by AS being set. It will then receive the address (A0-31) and the bytes selected in the byte mask (BSEL0-3). It then verifies the memory address (which should belong to the ad-

| Signal              | In | Out |

|---------------------|----|-----|

| RD <u>/WR</u>       | Х  |     |

| AS                  | Х  |     |

| DTACK               |    | Х   |

| ERR                 |    | Х   |

| D <sub>310</sub>    | X  | Х   |

| A <sub>310</sub>    | X  |     |

| Bsel <sub>3.0</sub> | X  |     |

Table III. Bus Lines Used by a Look-Aside Component

dress space of the component). If a write operation is requested, the data to be written should be available over the selected bytes of the data bus (D0-31). It will then output or receive data from Data0-31, according to the action specified by the RD/WR line. When the request has been fulfilled, the passive component will set DTACK. Finally, the AS line must be cleared.

Using this basic information about the bus lines, we show the specification and implementation of a look-aside component. This very simple model can be used as an exercise to show how new models can be incorporated into the existing hierarchy. When a read operation is issued, the look-aside component will return 1s in the data bits (D31-0) selected using the BSEL3-0 mask. If a write operation is issued, it returns an error. Look-aside components are attached to the bus like the memory. Table III shows the signals that should be used.

This atomic model can be defined as follows:

$$\begin{split} & \textit{SAMPLELA} = < X, S, Y, \textbf{d}_{int'} \textbf{d}_{ext'} \textbf{l}, D > \\ & \textit{X} = AS, \textit{RD}/\underline{WR}, A \ \hat{\textbf{I}} \ \{0, 4, \dots, 2^{3^2} - 1\}, \textit{BSEL} \ \hat{\textbf{I}} \ \{0, \dots, 2^4 - 1\}; \\ & \textit{S} = \textit{responseTime} \ \hat{\textbf{I}} \ \textbf{R}_0^+; \\ & \textit{Y=D} \ \hat{\textbf{I}} \ \{0, \dots, 2^{3^2} - 1\}, \textit{DTACK}, \textit{ERR}; \end{split}$$

In addition, the transition functions are described informally in Figure 7. As we can see, this component follows the bus specification, and is suitable for attachment to the bus in order to work as a passive component. This behavior is implemented on  $\delta ext()$ . It first senses a 1 over the AS line. The component then checks the address space in order to find out whether the request was for its address. In that case, it fills out the selected data bytes with 1's. Finally, the component waits for the active component to clear the AS line. When this happens, the *samplela* component sends a 0 over the DTACK line to end the communication. If we want to simulate a delay in the component's response, the atomic model must wait for some time before starting with the next step. Thus, we call the *hold\_in* procedure with the respective delay parameter. The output function  $\lambda()$  sends the signals over the output ports when needed. On the other hand,  $\delta int()$  performs just one operation, *passivate*. This means that the component remains inactive until a new signal arrives on any input port.

ACM Journal of Educational Resources in Computing, Vol. 1, No. 4, December 2001.

```

\delta \text{ext}() {

When (1 is received in the port AS)

if the value on received over A31..2 is in our address space then

if (RD/WR=1) then

if (BSEL0 = 1) then D7..0 := FFh

if (BSEL1 = 1) then D15..8 := FFh

if (BSEL2 = 1) then D23..16 := FFh

if (BSEL3 = 1) then D31..24 := FFh

DTACK:=1

else

ERR:=1

When (0 received in the port AS) and (1 sent in the port DTACK)

DTACK:=0;

hold_in(responseTime)

}

\deltaint() { passivate; }

λ() {

IF (D31..0 changed) send D31..0 over the D31..0 ports

IF (DTACK changed) send DTACK over the DTACK port

IF (ERR is changed) send ERR over the ERR port

```

Fig. 7. Behavior of the samplela look-aside component.

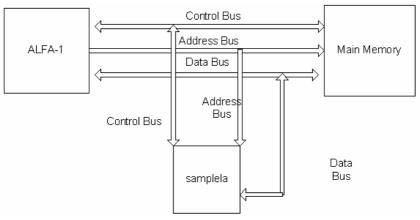

Fig. 8. Look-aside model interconnection.

Figure 9 shows part of the implementation of the transition functions using the CD++ tool. The first lines of the *externalFunction* ( $\delta ext($ )) identify the signal that has arrived. Since this function activates every time an input is received, we begin by identifying one signal at a time. We distinguish whether we are sending a response or waiting for a request using the *m\_state* variable. There are two arrays named *m\_ctlln* and *m\_ctlOut*, containing the present values of the input and output control ports. For instance, the

```

Model & sampleLA::externalFunction( const ExternalMessage & msg) {

string portName;

unsigned long portNum;

unsigned i;

// Get the port name where a message arrived, and its value

nameNum(msg.port().name(), portName, portNum );

for( i=0; i<NUM_CTL_IN_PORT; i++)</pre>

if ( portName == ctlInPortNames[i] )

m_ctlIn[i]= bit (msg.value());

if ( portName == string(addrInPortNames[0]) ){

m_addrIn[portNum] = bit (msg.value());

if (portName == bselInPortNames[0] )

m_bselIn[portNum] = bit (msg.value());

if (portName == dataInPortNames[0] )

m_dataIn[portNum] = bit (msg.value());

if (m_ctlIn[asin] && (m_state==waiting)) {

//If someone has requested a read/write operation to the bus

unsigned long addrRequested = fromBits(m_addrIn,m_addrWidth);

if ((m_minAddrSpaceLimit <= addrRequested) &&

(addrRequested < m_maxAddrSpaceLimit)) {

if (m_ctlIn[rwin] == 0) //if its trying to write to the model

m_ctlOut[errout].val = 1; //we send an error

else {

for (unsigned long i = 0 ; i< m_bselWidth; i++)</pre>

if (m_bselIn[i])

for (unsigned long j=0 ; j<m_byteSize ; j++)</pre>

m_dataOut[i*m_byteSize+j].val = 1;

m_ctlOut[dtackout].val = 1;

}

}

m_state = sending;

} else if (m_state == waiting) {

//If we do not receive an AS line we output 0 on dtack

m_ctlOut[dtackout].val = 0;

m_ctlOut[errout].val = 0;

m_state = waiting;

}

this->holdIn( active, m_responseTime );

}

Model & sampleLA::internalFunction( const InternalMessage & msg) {

this->passivate();

}

Model & sampleLA::outputFunction( const InternalMessage & msg) {

//Outputting data over the ports

for(unsigned i=0; i<NUM_CTL_OUT_PORT; i++)</pre>

if (needSend(m_ctlOut[i]))

this->sendOutput(msg.time(),*m_ctlOutPorts[i],m_ctlOut[i].val);

for(unsigned i=0; i<m_dataWidth; i++){</pre>

if (needSend(m_dataOut[i]))

this-

>sendOutput(msg.time(),*m_dataOutPorts[i],m_dataOut[i].val);

}

```

Fig. 9. CD++ samplela look-aside component implementation.

```

components: samplela

Link : OUT_A2@bus A2@samplela

...

Link : OUT_A31@bus A31@samplela

Link : OUT_DATA0@samplela IN_DATA0@cpu

...

Link : OUT_DATA31@samplela IN_DATA31@cpu

Link : OUT_DATA31@cpu IN_DATA0@samplela

...

Link : OUT_DATA31@cpu IN_DATA31@samplela

Link : OUT_DATA31@cpu IN_DATA31@samplela

Link : OUT_RD_WR@bus RW@samplela

Link : OUT_RD_WR@bus BSEL0@samplela

...

Link : OUT_BSEL0@bus BSEL0@samplela

```

Fig. 10. The iu.ma definition in Alfa-1.

[samplela]

responseTime = 0:0:0:0

minAddr = 65536

maxAddr = 131072

Fig. 11. Adding the atomic component samplela to the ALFA1.

*rwin* constant within the *m\_ctlIn* array represents the RD/WR port; hence, *m\_ctlIn[rwin]* will contain a 1 when the last input received on that port was 1. We only send data over the output ports if they have changed their values. Consequently, output ports (*m\_ctlOut*, *m\_dataOut*) are represented using a data type that distinguishes between the ones that need to be sent and the ones that do not. The *needSend* function is used to query whether a value needs to be sent. The value in the *val* field will be sent over the corresponding output port if needed. Finally, the *internalFunction* ( $\delta$ **int**) and the *outputFunction* ( $\lambda$ ) are straightforward implementations of the definitions in Figure 7. Once successfully compiled, the simulator will be able to reference the new component using the *samplela* name. The coupled model file of the Alfa-1 simulator (*iu.ma*) must be edited in order to include the new model in the hierarchy. The lines in Figure 10 should be added in the [top] model:

These definitions correspond to the bus connections of the *samplela* model. More precisely, following the original *iu.ma* connections, the address bus (A2-31), the BSEL signal, and the RD/WR are connected from the *bus* component to the *samplela* component. The DTACK line is connected the other way around (from *samplela* to *bus*). The data bus (D0-31) is connected directly from and to the *CPU* component; this connection is bidirectional due to the characteristics of this bus.

The *samplela* model has a response delay that can be configured using the *responseTime* atomic model parameter. This argument, as well as the address space boundaries *minAddr* and *maxAddr* (lower and higher bounds, respectively) will be passed to the model by adding the lines in Figure 11 at the end of the *iu.ma* file.

## 2.3. A Sample Look-Through Component

A look-through component (usually a cache memory) is inserted between the microprocessor and the bus, and it should be transparent to the other components attached to the bus. We will now include the specification of a very simple look-through component, which responds to read operations by returning 1's in the data bits selected by BSEL. If a write operation is intended, an error is raised.

Although it may seem similar to the look-aside component, this is not the case. This component is attached between the CPU and the bus, and it must be transparent to any other components when its address space its not being referenced.

The signals handled by a look-through component can be divided into those connected to the CPU and the ones connected to the bus. The lines connected to the CPU must react as a standard bus, whereas those connected to the bus must react as a CPU. In Table IV we show the input/output lines of this model, divided into the two types.

This atomic model can be defined as follows:

# **SAMPLELT** = $\langle X, S, Y, \mathbf{d}_{int}, \mathbf{d}_{ext}, \mathbf{l}, D \rangle$ .

$$\begin{split} \boldsymbol{X} &= AS(CPU), \ Busy_{in}(CPU), \ A_{in} \boldsymbol{\hat{I}} \{0, ..., 2^{32} - 1\}, BSEL_{in} \boldsymbol{\hat{I}} \{0, ..., 2^{3} - 1\}, \ RD\underline{WR}_{in}, \\ D_{in}(CPU) \boldsymbol{\hat{I}} \{0, ..., 2^{32} - 1\}, \ Err_{in}, \ DTACK_{in}, \ BGrant_{in}, \ Busy_{in}(bus), \ BGrant_{in'}, \\ D_{in}(bus) \boldsymbol{\hat{I}} \{0, ..., 2^{32} - 1\}; \end{split}$$

```

S = responseTime \ \hat{I} \ R_0^+;

```

$$\begin{split} \mathbf{Y} &= Err_{out} \ Dtack_{out} \ Busy_{out}(CPU), \ Busy_{out}(bus), \ Bgrant_{out} \ D_{out}(CPU) \ \widehat{\mathbf{I}} \ \{0, ..., 2^{32} - 1\}, \\ RD\underline{/WR}_{out} \ AS(BUS), A_{out} \ \widehat{\mathbf{I}} \ \{0, ..., 2^{32} - 1\}, \\ BSEL_{out} \ \widehat{\mathbf{I}} \ \{0, ..., 2^{3} - 1\}, \\ D_{out}(BUS) \ \widehat{\mathbf{I}} \ \{0, ..., 2^{32} - 1\}, \\ \end{array}$$

In addition, the transition functions are described informally in Figure 12. We can see that these transition functions are similar to the ones in the *samplela* component. The  $\delta$ **ext**() functions are the same when the address of the request is in the address space of the *samplelt* component. When the address is referencing another component, the *samplelt* component produces three state changes. First, it takes over the bus. Second, it forwards all of the input signals (data, address, RD/WR, AS, DTACK, ERR) from the CPU to the bus. Third, when the communication has ended, it releases the bus and stops forwarding the signals.

The implementation of these functions using CD++ can be found in the distribution files of the Alfa-1 computer. We have used similar implementation techniques to those used in *samplela*. A variable named  $m_forwardingState$  is used to distinguish among the three forwarding states previously identified. In this case, the code that copies the input

|                    |    | CPU |        |    | Bus |        |

|--------------------|----|-----|--------|----|-----|--------|

| Signal             | In | Out | In/Out | In | Out | In/Out |

| Err                |    | Х   |        | Х  |     |        |

| Dtack              |    | Х   |        | Х  |     |        |

| AS                 | Х  |     |        |    | Х   |        |

| RD/WR              | Х  |     |        |    | Х   |        |

| Busy               |    |     | Х      |    |     | Х      |

| Bgrant             |    | Х   |        | Х  |     |        |

| A <sub>312</sub>   | Х  |     |        |    | Х   |        |

| BSEL <sub>30</sub> | Х  |     |        |    | Х   |        |

| D <sub>310</sub>   |    |     | Х      |    |     | Х      |

Table IV. Input/Output Lines of a Look-Through Model

Values to the output ports (which takes place if the component is forwarding signals between the bus and the CPU) has been moved into the external function. This way it will be executed only once, when it is needed.

The look-through component must be attached between the CPU and the bus. To do so, we must first detach the CPU component from the bus (shown in Figure 13), and we must connect every line at both sides of the *samplelt* component (as described in Figure 14). Assuming that the new component has been compiled into the simulator and that its name is *samplelt*, we can change the coupling scheme by editing the coupled model file of the Alfa-1 (*iu.ma*). In this case, the lines in Figure 13 should be removed from the *top* model. The lines removed from the *top* model should be replaced by the lines in Figure 14.

After defining this simple look-through component, we can model a complete cache memory. A cache is a small amount of fast memory that reduces the overhead in accessing main memory by storing the most recently used cells. Whenever the CPU needs to perform operations with data stored in the cached cells, the cache memory will be accessed transparently. The decision about which main memory cells should be cached and which should not is made dynamically. In order to enable cached memory cells to change as a program runs, the cache memory includes some information about its contents in a directory. This index stores the main memory addresses of the cached cells. It also includes information to define which cells should be removed from the cache when we need to allocate new cells and there is no space left. There are several cache strategies to translate address bus requests into cache data. The two most widely used are direct and associative mapping (which uses associative memory to do the. translation). The most common replacement strategies are the least-recently-used, leastfrequently-used, first-in-first-out, and random [Tanenbaum 1999]. The two most common strategies to update the main memory are to update every change to the cached cells (write-through cache) or not (write-back cache). In the latter case, the cache memory needs to flush cached cells back to the main memory before they can be replaced.

We have developed a model representing a cache memory with write-back update. It is implemented as an extension to the look-through component defined earlier in this section.

```

\delta ext() {

When (1 is received in the port AS(CPU))

if the value on received over Ain31..2 is in our address space

then

if (RD/WRin=1) then

if (BSELin0 = 1) then Dout(CPU)7..0 := FFh

if (BSELin1 = 1) then Dout(CPU)15..8 := FFh

if (BSELin2 = 1) then Dout(CPU)23..16 := FFh

if (BSELin3 = 1) then Dout(CPU)31..24 := FFh

DTACKout:=1

else

ERRout:=1

When (0 is received in AS(CPU)) and (1 is sent in port DTACK-

out)

DTACKout:=0;

else

wait for BGRANT(BUS)=0

wait for BUSYin(BUS)=0

BUSYout(BUS):=1

start forwarding

wait for DTACKin(BUS)=1

DTACKout(CPU):=1

wait for AS(CPU)=0

AS(BUS):=0

BUSYout(BUS):=0

stop forwarding

DTACKout(CPU):=0

hold_in(responseTime)

δint() { passivate; }

\lambda() {

IF we are forwarding

Dout(CPU)31..0:=Din(bus)31..0

Dout(bus)31..0:=Din(CPU)31..0

Aout31..2:=Ain31..2

Bselout3..0:=Bselin3..0

Errout:=Errin

Dtackout:=Dtackin

Asout:=Asin

RD/WRout:=RD/WRin

IF (Dout(CPU)31..0 changed) send Dout(CPU)31..0

IF (Dout(bus)31..0 changed) send Dout(bus)31..0

IF (DTACKout changed) send DTACKout

IF (ERRout changed) send ERRout

```

Fig. 12. Behavior of the samplelt look-through component.

All the steps required to implement this model are included in the tool package, enabling users to gain experience with cache memory models. The model is designed to be changed easily without reprogramming the whole model. The associative mapping scheme with a FIFO replacement strategy is thoroughly tested. At present, LFU, LRU, and random replacement strategies are provided as in-progress developments.

| Link | : | OUT_DATA0@cpu IN_DATA0@mem   |

|------|---|------------------------------|

| Link | : | OUT_DATA31@cpu IN_DATA31@mem |

| Link | : | AS@cpu IN_AS@bus             |

| Link | : | RD_WR@cpu IN_RD_WR@bus       |

| Link | : | A0@cpu IN_A0@bus             |

| Link | : | A31@cpu IN_A31@bus           |

| Link | : | BSEL0@cpu IN_BSEL0@bus       |

| Link | : | BSEL3@cpu IN_BSEL3@bus       |

|      |   |                              |

Fig. 13. Removing connections to define a new coupling scheme.

| Link | : | OUT_DATA0@cpu IN_DATA_CPU0@samplelt   |

|------|---|---------------------------------------|

| Link | : | OUT_DATA31@cpu IN_DATA_CPU31@samplelt |

| Link | : | OUT_DATA0@samplelt IN_DATA_CPU0@cpu   |

| Link | : | OUT_DATA31@samplelt IN_DATA_CPU31@cpu |

| Link | : | AS@cpu IN_AS@samplelt                 |

| Link | : | RD_WR@cpu IN_RW@samplelt              |

| Link | : | A0@cpu IN_A0@samplelt                 |

| Link | : | A31@cpu IN_A31@samplelt               |

| Link | : | BSEL0@cpu IN_BSEL0@samplelt           |

| Link | : | BSEL3@cpu IN_BSEL3@samplelt           |

| Link | : | OUT_DATA_BUS0@samplelt IN_DATA0@mem   |

| Link | : | OUT_DATA_BUS31@samplelt IN_DATA31@mem |

| Link | : | AS@samplelt IN_AS@bus                 |

| Link | : | OUT_RW@samplelt IN_RD_WR@bus          |

| Link | : | OUT_A0@samplelt IN_A0@bus             |

| Link | : | OUT_A31@samplelt IN_A31@bus           |

| Link | : | BSELO@samplelt IN_BSELO@bus           |

| Link | : | BSEL3@samplelt IN_BSEL3@bus           |

Fig. 14. New links to connect a new component.

Fig. 15. Cache memory atomic abstraction level.

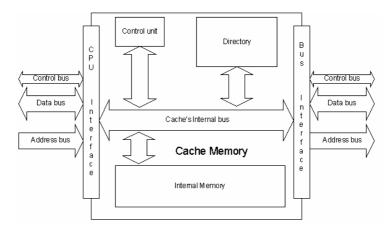

The first step to consider when defining a new component is how to design the model and the abstraction levels. At the highest level of abstraction, we see the cache as a single component interacting with the CPU and the bus. In order to achieve this behavior, the model follows the standard behavior of the look-through cache previously described. A second level of abstraction considers the internal organization of the cache.

Fig. 16. Cache memory structure.

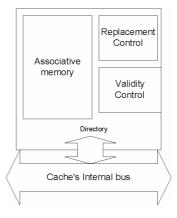

Fig. 17. Directory structure.

We divide the component into five subcomponents connected to two interfaces: one to handle bus communication and the other to handle CPU communication. An internal memory stores cached data, and a directory stores the main memory cells being cached (Figure 15). A control unit coordinates the operation of the other components (Figure 16). A third level of abstraction considers dividing the directory into three components: an associative memory to store the memory address of the cached memory; a replacement control component; and a validity component (see Figure 17). The validity module recognizes which cells have been updated in main memory.

## 3. THE ARCHITECTURE LEVEL

As explained in Section 1, Stallings [1999] defines computer architecture as those attributes that have a direct impact on the logical execution of a program. Examples of architectural attributes include the instruction set, the number of bits used to represent various data types (e.g., numbers, characters), I/O mechanisms, and techniques for addressing memory. For example, whether a computer will have a multiply instruction is an architectural design issue.

The Alfa-1 architecture is based in the description of the SPARC processor [Sun 2001]. This processor is provided with 520 integer registers divided into windows of 24 registers each, including input, output, and local registers for each procedure. When a procedure starts, 16 registers are reserved (8 local and 8 for output), and the 8 output records of the calling procedure are used as inputs. A specialized 5-bit register, called *CWP* (circular window pointer), marks the active window in the register ring. *CWP* is decremented each time a new procedure is started. The 32-bit *WIM* register (window invalid mask, one bit per window) avoids the superposition of a window in use by another procedure. When *CWP* is decremented, the hardware checks whether *WIM* is on the new window, and if so, an interrupt is raised. The interrupt service routine saves the content of the window, which will be overwritten. Usually, *WIM* has only a single bit set to 1, marking the oldest window. When that window is reached, the *WIM* rotates one unit. The processor status register includes the result of the last executed instruction. Its contents are interpreted as shown in Table V.

The memory is organized using byte addressing and the Little-Endian standard to store integers. The processor issues a memory access operation by writing an address (and data, if needed) to the bus.

As explained in the Organization section, there is a trap base register used to implement hardware and software interrupts. The register points to a memory address that contains the location of the trap routines. This location is organized as a table whose first 20 bits (trap base address) store the base address of the trap table (Table VI). When an interrupt request is received, the number of the trap to be serviced is stored in the bits 11..4. Therefore, the TBA points to the table position containing the address of the service routine. The last 4 address bits are 0 to guarantee at least 16 bytes to store each routine.

The computer emulates a reduced version of the *instruction set* level of the SPARC architecture. This processor uses instructions with a fixed size of 32 bits, with 8, 16, or 32 bit operands. There are two basic *Load/Store* operations, classified according to the size and sign of their operands. Arithmetic and Boolean operations include *add*, *and*, *or*, *div*, *mul*, *xor*, *xnor*, and *shift*. Several *jump* instructions are available, including *relative* jumps, *absolute* jumps, *traps*, *calls*, and *return* from traps. Other instructions include changing the movement of the register window, NOPs, and read/write operations on the PSR. There are two execution modes: user and kernel. Certain instructions can only be executed in kernel mode. In addition, the base and size registers are used only when the program is running in user mode.

After installing the tool, the computer is ready to run executable code for the SPARC processor. The first step in developing a program for execution is to write the source code using the SPARC Assembly Language [Sun 2001]. The source code must then be

| Bits  | Content                       | Description                               |

|-------|-------------------------------|-------------------------------------------|

| 31-24 | Reserved                      |                                           |

| 23    | N – Negative                  | 1 when the last operation is negative     |

| 22    | Z – Zero                      | 1 when the last operation is zero         |

| 21    | V – Overflow                  | 1 when the last operation is overflow     |

| 20    | C – Carry                     | 1 when the last operation carried one bit |

| 19-12 | Reserved                      |                                           |

| 11-8  | PIL-Processor Interrupt Level | Lowest interrupt number to be serviced.   |

| 7     | S – State                     | 1= Kernel mode; 0=User mode.              |

| 6     | PS – Previous State           | Last mode.                                |

| 5     | ET – Enable Trap              | 1=Traps enabled; 0=Traps disabled.        |

| 4-0   | CWP                           | Points to the current register window.    |

## Table V. Contents of the Processor Status Register

Table VI. Contents of the Trap Base Address Table

| Bits | Content           | Description                    |

|------|-------------------|--------------------------------|

| 3112 | Trap base address | Base address of the Trap table |

| 114  | Тгар Туре         | Trap to be serviced            |

| 30   | Constant (0000)   |                                |

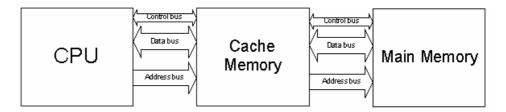

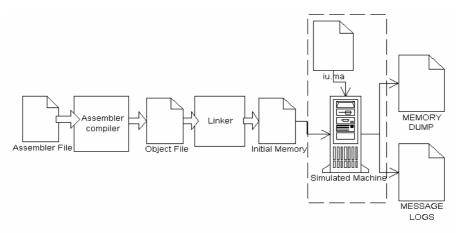

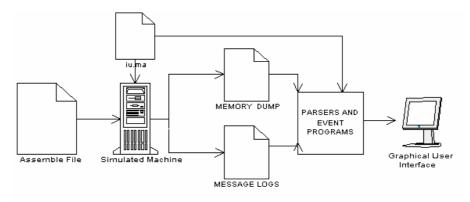

Fig. 18. Process of simulation from the assembler file to the memory dump.

assembled and linked. The resulting executable file must be loaded as a memory image in the simulated computer's memory. Then the simulation tool should be activated. Once the program has ended, the memory contents can be dumped and the memory values can be checked. While the simulation is executing, a detailed log file records component activity, allowing the analysis of changes in the state variables contained in the memory, processor, or bus components. Figure 18 sketches these procedures.

The first lines in Figure 19 show parts of a program written in the SPARC Assembly Language. The second part (Initial Image) gives binary code generated when assembled, along with the absolute addresses for each instruction or data (one word each).

| <pre>1 Partial and special copy of a string. r1 : offset over source 1 r2 : character to copy. r3 : offset over dest cycle: lduh [%r1*source], %r2</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                 |           |            |            |            |         |          |          |       |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------|------------|------------|------------|---------|----------|----------|-------|--|--|

| cycle:       lduh [\$rl+source], \$r2       ! Load unsigned halfword         jmpl routine, \$r6       ! Jump and link         inc 2, \$r1       ! Delay slot         inc 4, \$r3       ! next character         subcc \$rl, 12, \$r0       ! next position over dest         mop       ! Repeat the Cycle 6 times         nop       ! Delay Slot         subcc \$rl, 12, \$r0       ! Delay Slot         source:       .ascii *       ! Source string         dest:       .ascii *       :         .ascii *       :       ! Source string         dest:       .ascii *       :         .ascii *       :       :         .ddr. Memore       :       : <t< td=""><td colspan="11">! Partial and special copy of a string. r1 : offset over source</td></t<>                                                                                                                                                            | ! Partial and special copy of a string. r1 : offset over source |           |            |            |            |         |          |          |       |  |  |

| cycle:       lduh [\$rl+source], \$r2       ! Load unsigned halfword         jmpl routine, \$r6       ! Jump and link         inc 2, \$r1       ! Delay slot         inc 4, \$r3       ! next character         subcc \$rl, 12, \$r0       ! next position over dest         mop       ! Repeat the Cycle 6 times         nop       ! Delay Slot         subcc \$rl, 12, \$r0       ! Delay Slot         source:       .ascii *       ! Source string         dest:       .ascii *       :         .ascii *       :       ! Source string         dest:       .ascii *       :         .ascii *       :       :         .ddr. Memore       :       : <t< td=""><td>! r2 :</td><td>character</td><td>to copy.</td><td>r3 : off</td><td>set over d</td><td>lest</td><td></td><td></td><td></td></t<>                                                                                                                   | ! r2 :                                                          | character | to copy.   | r3 : off   | set over d | lest    |          |          |       |  |  |

| jmpl routine, %r6         ! Jump and link           sth %r2, [%r3+dest]         ! Delay slot           inc 2, %r1         ! next character           inc 4, %r3         ! next position over dest           bhe cycle         ! next position over dest           unimp         ! Polay Slot           routine:jmp %r6+8         ! Source string           ascii "         .           .ascii " <t< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td>ungiane</td><td>d halfw</td><td>ord</td></t<>                                                                                                                                              |                                                                 |           |            |            |            |         | ungiane  | d halfw  | ord   |  |  |

| sth %r2, [%r3+dest]         ! Delay slot           inc 4, %r3         ! next character           inc 4, %r3         ! next position over dest           subcc %r1, 12, %r0            bnc cycle         ! Repeat the Cycle 6 times           nop         ! Delay Slot           subcc %r1, [%r3+dest2]         ! Delay Slot           source:         ascii "         '           .ascii "         '           .ddr.                                                                                                                                                                                                                                                                        | C/CIC:                                                          | -         |            | , 012      |            |         |          |          | JIG   |  |  |

| <pre>inc 2, %r1</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                 |           |            | 1          |            |         |          | v        |       |  |  |

| inc 4, %r3 ! next position over dest<br>subcc %r1, 12, %r0 ! Repeat the Cycle 6 times<br>nop<br>unimp<br>routine: jmg %r6+8 ! Delay Slot<br>source: .ascii "xxxx String of text xxxx" ! Source string<br>dest: .ascii "                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                 |           |            | C ]        |            |         |          |          |       |  |  |

| subcc %r1, 12, %r0         ! Repeat the Cycle 6 times           nop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                 |           |            |            |            |         |          |          |       |  |  |

| bme cycle         ! Repeat the Cycle 6 times           nop         nop           radius         still           still         [k3+dest2]           source:         .ascii *           .ascii *         *           .d                                                                                                                                                                                                                                                                                                                      |                                                                 | inc 4, %  | r3         |            |            | ! next  | positio  | n over o | lest  |  |  |

| nop         unimp           routine:jmp %r6+8         st %r1, [%r3+dest2]         ! Delay Slot           source:.ascii "xxxx String of text xxxx"         ! Source string           dest:         .ascii "         "           .ddt 1000100         01100000         1000100           .ddt 1000010         01100000         substract 12 to R0           .ddt 01000001111111 <td></td> <td>subcc %r</td> <td>l, 12, %r(</td> <td>C</td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                        |                                                                 | subcc %r  | l, 12, %r( | C          |            |         |          |          |       |  |  |

| nop         unimp           routine:jmp %r6+8         st %r1, [%r3+dest2]         ! Delay Slot           source:.ascii "xxxx String of text xxxx"         ! Source string           dest:         .ascii "         "           .ddt 1000100         01100000         1000100           .ddt 1000010         01100000         substract 12 to R0           .ddt 01000001111111 <td></td> <td>bne cycle</td> <td>5</td> <td></td> <td></td> <td>! Repea</td> <td>at the C</td> <td>vcle 6</td> <td>times</td>                                                                                                                       |                                                                 | bne cycle | 5          |            |            | ! Repea | at the C | vcle 6   | times |  |  |

| unimp           routine:jmp %r0+8           source: .ascii "xxxx String of text xxxx"         ! Delay Slot           source: .ascii "xxxx String of text xxx"         ! Source string           dest: .ascii "         "           .ddr. Memory Image         Incet ratter           .ddr. 100010 001010000 01100000000000000000                                                                                                                                                                                                                                                                     |                                                                 | -         |            |            |            | -       |          | -        |       |  |  |

| routine:jmp %r6+8<br>st %r1, [%r3+dest2] ! Delay Slot<br>! Source: .ascii "xxxx String of text xxxx" ! Source string<br>dest: .ascii " " "<br>.ascii " " " " " " "<br>.ascii " " " " " " " "<br>.ascii " " " " " " " "<br>.ascii " " " " " " " "<br>.322 1000100 00100000 01100000 0100000 000000                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                 | -         |            |            |            |         |          |          |       |  |  |

| st %t). (%r3+dest2)         ! Delay Slot           source: .ascii "xxxx String of text xxxx"         ! Source string           dest: .ascii "         "           dest: .ascii "         "           .asci "         "           .asci "         "           .dest !         !           .dest !         !           .dest !         !                                                                                                                                                                                                                                                                                            | routino                                                         | -         | 0          |            |            |         |          |          |       |  |  |

| source: .ascii "xxxx String of text xxxx"         ! Source string           dest: .ascii "         "           .asci "         "                                                                                                                                                                                                                                                                                                                          | routine                                                         |           |            | 1          |            | L Dalas |          |          |       |  |  |