# **Computer System Modeling**

## **At The Hardware Platform Level**

by

Amir Saghir

A thesis submitted to the

Faculty of Graduate Studies and Research in partial fulfilment of the requirements for the

degree of

Master of Applied Sciences

In Electrical Engineering

Ottawa-Carleton Institute of Electrical and Computer Engineering

Faculty of Engineering

Department of Systems and Computer Engineering

Carleton University

September 2002

The undersigned hereby recommend to the Faculty of Graduate Studies and Research the acceptance of the thesis

# "Computer System Modeling At The Hardware Platform Level"

Submitted By

#### **Amir Saghir**

In Partial Fulfillment of the Requirements for the Degree of Master of Applied Science

Dr. Gabriel Wainer (Thesis Co-supervisor) Dr. Trevor Pearce (Thesis Co-supervisor)

Dr. Rafik Goubran (Department Chair, Systems and Computer Engineering)

> Department of Systems and Computer Engineering Faculty of Engineering, Carleton University

> > September 2002

# **Abstract**

Modeling and simulation plays an important role in the development of computer systems. This research work focuses on modeling general computer hardware platforms using the Discrete Event system Specification (DEVS) modeling formalism, and mapping these models onto the High Level Architecture (HLA) for simulation interoperability.

An HLA-based system level framework for a general hardware platform is proposed, in which hardware component details are modeled using DEVS atomic models. To verify the proposed framework, a case study is presented for a simplified Intel 8088 processor based platform. The components modeled in this case study are a processor, a memory module, an interrupt controller, a bus controller and a timer.

This research has developed an approach that flattens the modeling hierarchy by using only DEVS atomic models mapped onto the HLA. As a result, the simulation support layer normally present to handle coupled models is not needed. The general hardware platform framework influences aspects of component models, and these aspects are identified and related to their implications to the HLA. This work has laid some groundwork leading towards a simulation tool for hardware platform modeling and simulation that can be used by system designers during the product development phase.

## **Acknowledgements**

I express my heartiest and most sincere gratitude to my supervisors Dr. Trevor Pearce and Dr. Gabriel Wainer for their help, supervision, and full support towards the completion of this thesis.

Needless to say, I am grateful to my parents and my dear wife for providing me all the emotional support and encouragement.

## **TABLE OF CONTENTS**

| ABSTRACT III                             |

|------------------------------------------|

| LIST OF ACRONYMS                         |

| LIST OF FIGURES                          |

| LIST OF TABLES                           |

| CHAPTER 1                                |

| INTRODUCTION 1                           |

| CHAPTER 2                                |

| BACKGROUND FOR THE DEVS AND THE HLA 4    |

| 2.1 System Development Method 4          |

| 2.2 THE DEVS FORMALISM                   |

| 2.2.1 Atomic Model 5                     |

| 2.2.2 Coupled Model                      |

| 2.3 HIGH LEVEL ARCHITECTURE (HLA)        |

| 2.3.1 Runtime Infrastructure (RTI)       |

| 2.3.1.1 Components of the RTI9           |

| 2.3.1.2 Management Areas of RTI 10       |

| CHAPTER 3                                |

| STATE OF THE ART IN THE DEVS/HLA 12      |

| 3.1 IMPLEMENTATION OF THE DEVS FORMALISM |

| 3.2 DEVS IMPLEMENTATION OVER THE HLA/RTI |

| 3.2.1 DEVS Modeling using DEVS-C++       |

| 3.2.2 The Parallel DEVS (PDES) Protocol           | 14 |

|---------------------------------------------------|----|

| 3.2.3 Mapping of the PDES Protocol to the HLA/RTI | 16 |

| CHAPTER 4                                         |    |

| MODELING HARDWARE PLATFORMS                       |    |

| CHAPTER 5                                         |    |

| SIMULATION FRAMEWORK AND DEVS ATOMIC MODELS       |    |

| 5.1 System Level Block diagram                    |    |

| 5.1.1 System Level Flow Diagram for a Federate    |    |

| 5.1.2 DEVS Atomic Models for each Federate        |    |

| 5.1.2.1 MEMORY MODULE                             |    |

| 5.1.2.2 PROCESSOR MODULE                          |    |

| 5.1.2.2.1 Bus Interface Unit (BIU)                | 32 |

| 5.1.2.2.2 Execution Unit (EU)                     | 34 |

| 5.1.2.2.3 Control Unit (CU)                       | 36 |

| 5.1.2.3 BUS CONTROLLER MODULE                     |    |

| 5.1.2.4 INTERRUPT CONTROLLER MODULE               | 38 |

| 5.1.2.5 TIMER MODULE                              | 39 |

| CHAPTER 6                                         |    |

| CASE STUDY                                        | 41 |

| 6.1 INTRODUCTION                                  | 41 |

| 6.1.1 Case study program                          |    |

| 6.2 SIMULATOR IMPLEMENTATION                      |    |

| 6.2.1 System level Block diagram                  |    |

| 6.2.1.1 Level of abstraction for the simulator's timing    | 44 |

|------------------------------------------------------------|----|

| 6.2.1.2 Algorithm to start the simulation                  | 45 |

| 6.2.1.3 Stopping the simulation                            |    |

| 6.2.1.4 Communication among Modules/Federates              | 46 |

| 6.2.1.5 Time elapse using RTI                              | 47 |

| 6.2.1.6 Logging simulator activity                         |    |

| 6.2.1.7 FOM/SOM                                            |    |

| 6.2.2 Memory Module                                        |    |

| 6.2.2.1 Assumptions                                        |    |

| 6.2.2.2 Development of Memory module                       | 50 |

| 6.2.2.2.1 External transition function $(\delta_{ext})$    | 50 |

| 6.2.2.2.2 Duration function (ta)                           | 53 |

| 6.2.2.2.3 Output function (λ)                              | 54 |

| 6.2.2.2.4 Internal transition function ( $\delta_{int}$ )  | 54 |

| 6.2.2.2.5 Confluent transition function ( $\delta_{con}$ ) | 54 |

| 6.2.2.3 Interaction between Memory module and the RTI      | 55 |

| 6.2.2.4 Software Flow diagram                              | 56 |

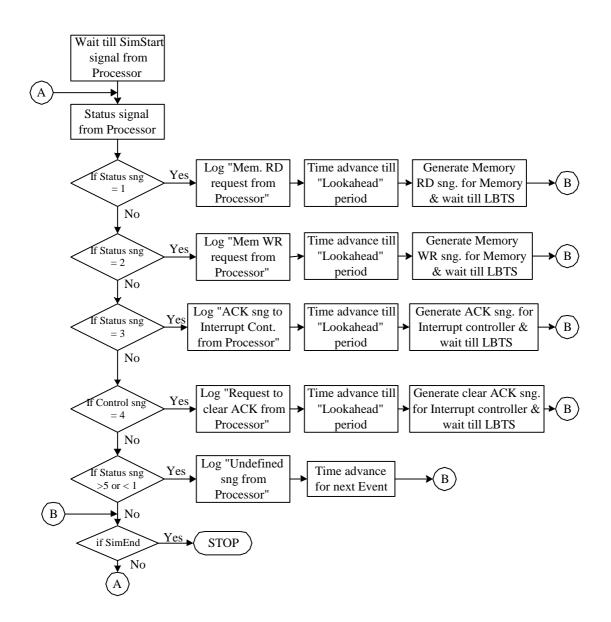

| 6.2.3 Processor Module                                     | 56 |

| 6.2.3.1 Assumption                                         | 57 |

| 6.2.3.2 Internal Registers of the processor module         | 57 |

| 6.2.3.3 Resolution of the interrupt request (INTR) signals | 58 |

| 6.2.3.4 Software Flow diagram                              | 59 |

| 6.2.4 Bus Controller Module                                | 59 |

| 6.2.4.1 Assumption                                | 60 |

|---------------------------------------------------|----|

| 6.2.4.2 Software Flow diagram                     | 60 |

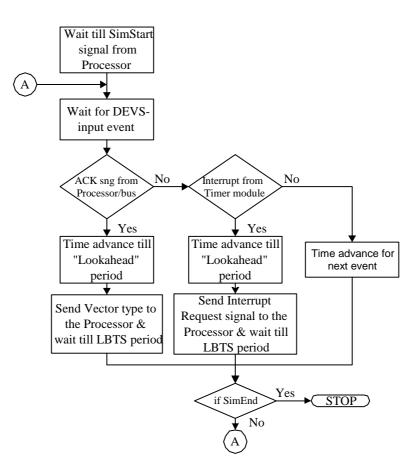

| 6.2.5 Interrupt Controller Module                 | 61 |

| 6.2.5.1 Assumption                                | 62 |

| 6.2.5.2 Software Flow diagram                     | 62 |

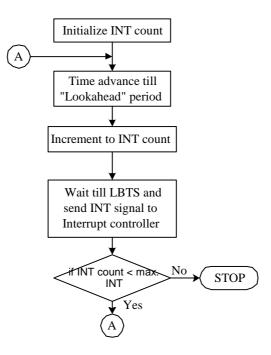

| 6.2.6 Timer Module                                | 63 |

| 6.2.6.1 Assumption                                | 63 |

| 6.2.6.2 Software Flow diagram                     | 64 |

| CHAPTER 7                                         |    |

| RESULTS                                           | 65 |

| 7.1 MODULE LOG INTERPRETATIONS                    | 66 |

| 7.1.1 Processor's Log                             | 66 |

| 7.1.2 Memory module's Log                         | 67 |

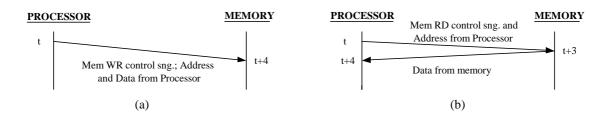

| 7.2 Message Event Sequence in Minimum Mode        | 68 |

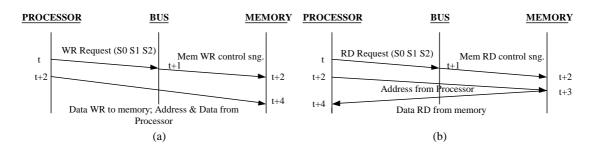

| 7.2.1 Memory RD and Memory WR Operations          | 69 |

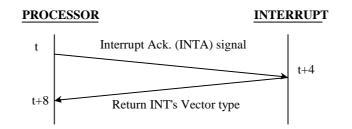

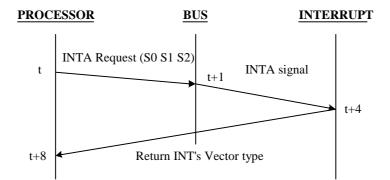

| 7.2.2 Interrupt acknowledge Operation             | 69 |

| 7.3 Message Event Sequence in Maximum Mode        |    |

| 7.3.1 Memory RD and Memory WR Operations          | 70 |

| 7.3.2 Interrupt acknowledge Operation             |    |

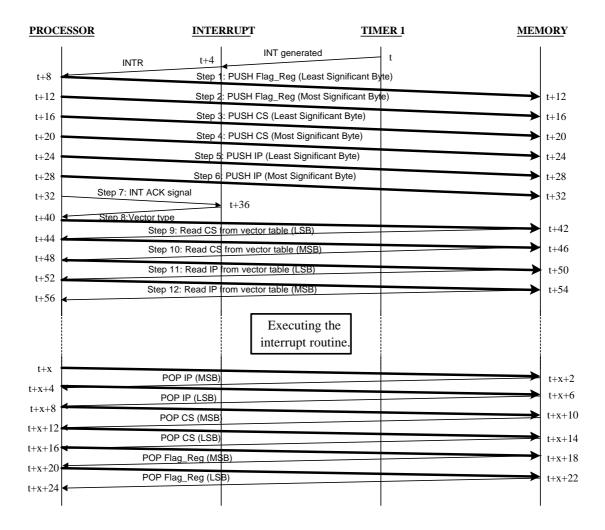

| 7.4 SEQUENCE DIAGRAM FOR INTERRUPT CALL OPERATION | 71 |

| 7.5 Analysis of the results                       |    |

| CHAPTER 8                                         |    |

| CONCLUSIONS                                       |    |

| 8.1 Conclusions                                        | 76 |

|--------------------------------------------------------|----|

| 8.2 SUMMARY OF CONTRIBUTIONS                           | 77 |

| 8.3 FUTURE RESEARCH                                    | 78 |

| REFERENCES                                             | 80 |

| APPENDIX A                                             | 82 |

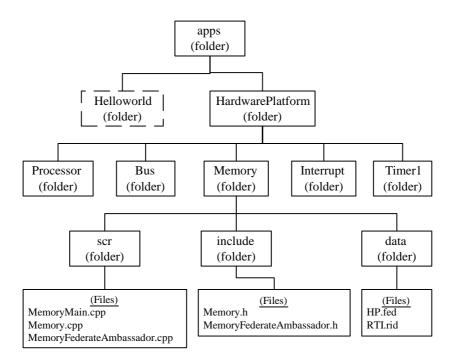

| SIMULATOR'S DIRECTORY STRUCTURE & SOFTWARE CODE IN C++ | 82 |

| A.1 DIRECTORY STRUCTURE                                | 82 |

| A.2 SOFTWARE CODE IN C++                               | 83 |

| APPENDIX B                                             | 85 |

| LOG FILES FOR EACH FEDERATE                            | 85 |

## List of Acronyms

| BIU     | Bus Interface Unit                  |

|---------|-------------------------------------|

| CU      | Control Unit                        |

| CS      | Code Segment                        |

| DEVS    | Discrete Event System Specification |

| DS      | Data Segment                        |

| EA      | Effective Address                   |

| EU      | Execution Unit                      |

| FED     | Federation Execution Data           |

| FedExec | The Federation Executive            |

| FOM     | Federation Object Model             |

| HLA     | High level Architecture             |

| IF      | Internal Flags                      |

| INTA    | Interrupt Acknowledge               |

| INTR    | Interrupt Request                   |

| IP      | Instruction Pointer                 |

| LBTS    | Lower Bound Time Stamp              |

| LibRTI  | The RTI library                     |

| LSB     | Least Significant Byte              |

| MSB     | Most Significant Byte               |

| OMDT    | Object Model Development Tool       |

| RO      | Receive Order                       |

| RTI     | Run time Infrastructure |

|---------|-------------------------|

| RtiExec | The RTI Executive       |

| SOM     | Simulation Object Model |

| SP      | Stack Pointer           |

| SS      | Stack Segment           |

| TSO     | Time Stamped Order      |

## **List of Figures**

| Figure 1: Systematic representation of a basic (atomic) model                           |

|-----------------------------------------------------------------------------------------|

| Figure 2: RTI Major Components. [8]9                                                    |

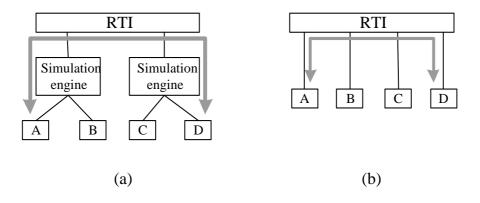

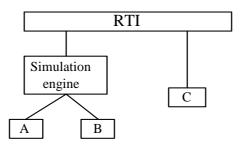

| Figure 3: Layered approach to implement the DEVS/HLA. [2]                               |

| Figure 4: The Parallel DEVS simulation protocol [2]16                                   |

| Figure 5: Coordinator as a Federate (the PDES protocol mapping into the HLA) [2] 17     |

| Figure 6: The block diagram for basic approach from chapter 3 19                        |

| Figure 7: A Model of the proposed solution                                              |

| Figure 8: System-level block diagram for Hardware platform simulator                    |

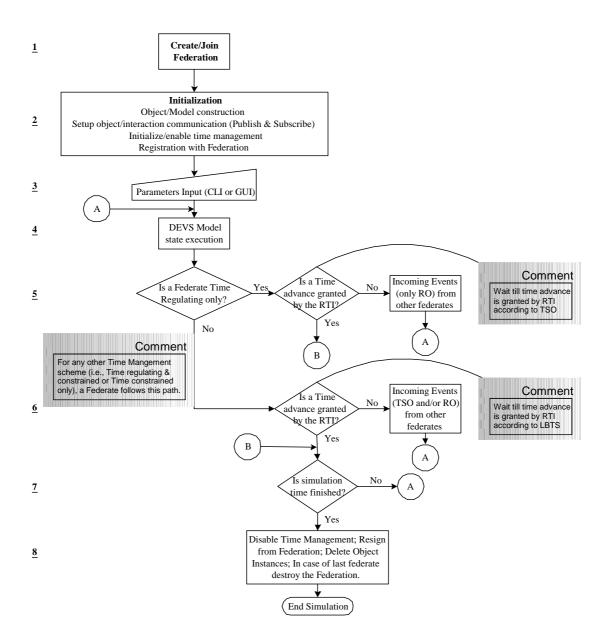

| Figure 9: Simulation flow chart of a federate25                                         |

| Figure 10: State diagram for memory read and write for minimum operation mode 31        |

| Figure 11: Block diagram showing sub-modules in a Processor model                       |

| Figure 12: System level block diagram implemented for the case study                    |

| Figure 13: Creating an AHVPS for communication among Module/Federates                   |

| Figure 14: Time elapse requested by a Federate using the RTI service methods            |

| Figure 15: Block diagram containing time management and attribute information 49        |

| Figure 16: Memory map for 8-bit structure (specific to the case study) 50               |

| Figure 17: Implementation of the external transition function in the simulation code 53 |

| Figure 18: Implementation of the duration function in the simulation code               |

| Figure 19: Implementation of the output function in the simulation code                 |

| Figure 20: Flow Chart of the memory module                                              |

| Figure 21: Flow chart of the processor module 59                                        |

| Figure 22: Flow diagram of the bus controller module                                       |

|--------------------------------------------------------------------------------------------|

| Figure 23: Flow Chart of the interrupt controller module                                   |

| Figure 24: Flow chart of the timer module                                                  |

| Figure 25: Snap shot of Processor module's log                                             |

| Figure 26: Snap shot of Memory module's log 68                                             |

| Figure 27: (a) Memory Write (b) Memory Read operation in minimum mode 69                   |

| Figure 28: Interrupt acknowledge (INTA) operation in minimum mode 69                       |

| Figure 29: (a) Memory Write (b) Memory Read operation in maximum mode70                    |

| Figure 30: Interrupt acknowledge (INTA) operation in maximum mode                          |

| Figure 31: Interaction flow between different modules during Interrupt operation 72        |

| Figure 32: Snap shot of the Processor's log for the analysis of the MOV [BX],CH            |

| instruction73                                                                              |

| Figure 33: Snap shot of the Memory's log for the analysis of the MOV [BX],CH               |

| instruction74                                                                              |

| Figure 34: Snap shot of the Processor's log, showing the start of the execution of the POP |

| BX instruction74                                                                           |

| Figure 35: Snap shot of the Processor's log, showing the end of the execution of the POP   |

| BX instruction75                                                                           |

| Figure 36: (a) Hierarchical models using the HLA framework (b) Flat models using the       |

| HLA framework                                                                              |

| Figure 37: Combination of Flat and Hierarchical models using the HLA framework 79          |

| Figure 38: Simulator's directory structure. (This is one of many possible configurations). |

|                                                                                            |

## **List of Tables**

| Table 1: RTI Management Areas partitioned in FedExec life cycle [8]                  | . 11 |

|--------------------------------------------------------------------------------------|------|

| Table 2: Main program's opcodes for the case study                                   | . 42 |

| Table 3: Interrupt routine's opcodes for the case study                              | . 43 |

| Table 4: Decoding of the status signals $(S_0 S_1 S_2)$ by the bus controller module | . 60 |

# CHAPTER 1

# **Introduction**

The use of embedded computer systems to solve application problems requires an understanding of both the hardware platform involved and the software that customizes the hardware for the particular application. Modeling and simulation is used increasingly in developing the hardware and software of such systems. Modeling is required to represent a system for the purpose of studying the system. A simulation is the imitation of the operation of a system over time. The behavior of a system as it evolves over time is studied by developing a simulation model [3]. The models created by hardware engineers while developing hardware components often contain details that are irrelevant to software developers. Furthermore, the simulation of the hardware component models is often fine-grained and computationally intensive, since the states of all of the individual transistors in the components must be addressed. Software developers would prefer a programmer's model of the hardware platform, which would abstract away irrelevant hardware details and focus only on the information relevant to software development. Ideally, the more abstract programmer's models would have larger-grained simulations that are less computationally expensive than the hardware models.

The goal of this research is to develop a generic framework that can be extended to model and simulate specific computing platforms by introducing platform-specific details. Software developers can use these models to develop and test their software for computing platforms. For modeling platform components, the DEVS (Discrete event system specification) formalism is used. The simulation framework for these models is defined, following the specifications of the HLA (High-level architecture) standard. The rationale for adopting the DEVS/HLA approach is explained in chapter 4.

This research is seen as an initial step in a longer-term research project that will (later) include the development of tools to simplify the introduction of platform-specific details by handling the formal aspects associated with DEVS and the HLA (such tools would allow designers to focus more attention on the platform-specific details by relieving the designer of the unnecessary DEVS and HLA clutter).

A brief synopsis of the structure of the thesis document is as follows. Chapter 2 provides the background information about the DEVS formalism and the HLA. It briefly describes different classes of the DEVS formalism and key features of the HLA that are required to manage various aspects of the simulator. Chapter 3 reviews the latest ideas in the DEVS formalism and a subset of the tools developed to implement the DEVS formalism. It also describes a layered approach to use DEVS and the HLA for a simulator. Chapter 4 states the research motivation, a critical analysis of the facts of chapter 3, the research question under investigation, the approach adopted to answer the question and the scope of this research. Chapter 5 describes the proposed framework of the simulator and the general models of basic hardware platform components. These general models have a list of parameters, which can be used for defining the functionality of these components. Chapter 6 shows how this simulator can be used for a specific hardware platform. Execution of an example program (a few instructions of the 8088 processor) is simulated in order to illustrate the proposed DEVS/HLA approach. It also describes the flow charts of each hardware component used in the case study. Chapter 7 shows the results of the case study. Excerpts of some component logs are discussed and the message flow between different components is explained. These logs and message flows are helpful in verifying the simulator. Chapter 8 concludes the research. It discusses the contributions and suggests some future research topics. The conclusion is followed by the references and two appendices. Appendix A refers to the software code for each hardware component involved in the case study. Appendix B refers to each component's log in the case study.

# CHAPTER 2

# **Background for the DEVS and the** <u>HLA</u>

In this section a system development process is discussed with emphasis on the need for modeling as an initial step in development. Computer systems being discrete in nature require an appropriate modeling formalism and a simulation framework to get the system analyzed. This section describes the Discrete Event System Specification (DEVS) formalism to model various components of a computer system and the High-level architecture (HLA) as a simulation framework standard.

## 2.1 System Development Method

The products based on computer systems are increasing tremendously. In order to verify the required features of these computer systems, modeling is becoming an important part of product development. Modeling has various levels of abstraction and complexity that are normally used during the development cycle of a system.

Computer systems are discrete in nature. Much research effort has been made in order to find the most appropriate modeling formalism for such systems. One of the current approaches is the use of computer simulation to analyze these models and explore the properties of these systems. This modeling and simulation methodology is playing an important role in the development of computer platforms and systems.

## **2.2 The DEVS Formalism**

The DEVS (Discrete Event System Specification) is a system's formalism, with a welldefined concept of modularity and coupling of components. The DEVS formalism focuses on the changes of variable values and generates time segments that are piecewise constant. In essence the formalism defines how to generate new values for variables and the times the new values should take effect. An important aspect of the formalism is that the time intervals are continuous. There are two major classes from which all the userdefined models can be developed – atomic and coupled.

A brief description of the DEVS Atomic model and Coupled model is as below. [4]

#### 2.2.1 Atomic Model

An atomic model directly specifies the system's response to events on its input ports, state transitions, and the generation of events on its output ports. It is defined as [4]:

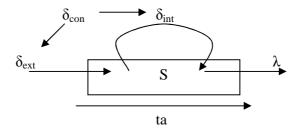

$AM = \langle IO, X, S, Y, \delta_{int}, \delta_{ext}, \delta_{con}, \lambda, ta \rangle$

Where

**IO** is the model's interface (input/output ports).

**X** is the input events set.

S is the state set.

Y is the output events set.

$\delta_{int}$  is the internal transition function.

$\delta_{ext}$  is the external transition function.  $\delta_{con}$  is the confluent transition function  $\lambda$  is the output function.

ta is the time advance function.

Figure 1: Systematic representation of a basic (atomic) model.

Figure 1 shows a graphical representation of an atomic model. Each model is provided with an interface consisting of input and output ports to communicate with other models. When an input arrives the instance variable S is updated. The  $\delta_{ext}$  function accepts the input and changes the instance variable. After an elapsed time, given by the ta function, the system checks the internal variables and makes internal changes to bring the system to the next state. The function that performs all this is the  $\delta_{int}$  function. The  $\delta_{con}$  function decides what to do when both external and internal events occur together. It might, for example, decide the order between the  $\delta_{ext}$  and the  $\delta_{int}$  functions. The  $\lambda$  function produces the output Y from the instance variables. The ta function returns the time to the next internal event.

#### **2.2.2 Coupled Model**

A DEVS coupled model is composed of several atomic or coupled sub-models. It is defined as [4]:

$CM = \langle IO, X, Y, D, \{Mi\}, \{Ii\}, \{Zij\} \rangle$

Where

**IO** is the model's interface (input/output ports).

**X** is the set of input events.

Y is the set of output events.

**D** is an index for the components of the coupled model.

Mi is a basic DEVS (that is, an atomic or coupled model).

**Ii** is the set of influencees of model i (that is, the models that can be influenced by outputs of model i).

**Zij:**  $Yi \rightarrow Xj$  is i to j translation function.

We can see that coupled models are defined as a set of basic components (atomic or coupled), which are interconnected through the models' interfaces. The influencees of a model define the models to which outputs must be sent. The translation function is in charge of converting the outputs of a model into inputs for the others. To do so, an index of influencees is created for each model (Ii). This index defines that the outputs of the model Mi are connected to the inputs in the model Mj, where j is an element of the set Ii.

## 2.3 High Level Architecture (HLA)

The HLA was developed by the US Department of Defense (DoD) based on a process involving government, industry and academia. The High Level Architecture (HLA) provides a general framework within which simulation developers can structure and describe their simulation application. In particular, the HLA addresses two key issues: promoting interoperability between simulations and aiding the reuse of models. In the terminology of the HLA [1]

- The combined simulation system created from the constituent simulation is a federation.

- Each simulation that is combined to form a federation is a federate.

The baseline of the HLA, defined in IEEE Standard 1516, includes the following:

- The HLA Rules define the responsibilities and relationships among the components of an HLA federation. [5]

- The HLA Interface Specification provides a specification of the functional interface between the HLA federates and the HLA Runtime Infrastructure (RTI) (RTI is discussed in section 2.3.1). This specification defines all the RTI services and identifies "callback" functions that must be provided by each federate. [6]

- The HLA Object Model Template (OMT) provides a common presentation format for HLA Simulation and Federation Object Models (SOM/FOM) [7]. A SOM defines the objects and interactions within a federate, while a FOM defines object models, communication between federates, condition for data updates and other information for interoperability purposes. The Federation Execution Data (FED), which is

required as an input to the RTI, is a subset of a FOM along with the specification of some default values for transport properties of data. In brief, the OMT provides an interface between the models and the RTI/HLA.

#### **2.3.1 Runtime Infrastructure (RTI)**

The RTI is a middleware that provides common services to federates and/or federations. It is an implementation of the HLA Interface Specification. The RTI software can be executed on a standalone computer or distributed over a network.

#### 2.3.1.1 Components of the RTI

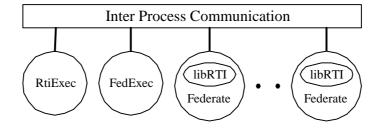

Figure 2 shows the major components of the RTI and each component is briefly discussed after the figure.

Figure 2: RTI Major Components. [8]

*The federation executive (FedExec)* manages multiple federates within a federation. It allows federates to join and to resign, and facilitates data exchange between participating federates. Each federate joining the federation is assigned a federation wide unique handle.

*The RTI Executive (RtiExec)* manages multiple federation executions in a network. It helps in initializing RTI components for each federation executive (FedExec). It also ensures that each FedExec has a unique name.

*The RTI library (libRTI)* provides the RTI services specified in the HLA Interface Specification to federate developers.

#### 2.3.1.2 Management Areas of RTI

The HLA Interface Specification divides the services provided by the RTI into six management areas. Table 1 summarizes the objectives of each of the management areas:

| Management Area        | Activities Supported                                          |

|------------------------|---------------------------------------------------------------|

| Federation Management  | Manages federation execution. Initializes name space,         |

|                        | transportation, routing spaces etc.                           |

| Declaration Management | Specifies the data a federate sends and/or receives.          |

| Object Management      | Creates, modifies and deletes objects and interactions.       |

|                        | Facilitates object registration and distribution. Coordinates |

|                        | attribute updates among federates. Accommodates various       |

|                        | transportation and time management schemes.                   |

| Ownership Management   | Supports transfer of ownership for individual object          |

|                        | attributes. Offers both "push" and "pull" based               |

|                        | transactions.                                                 |

| Time Management   | Establishes or associates events with federate time.         |

|-------------------|--------------------------------------------------------------|

|                   | Regulates interactions, attribute updates, object reflection |

|                   | or object deletion by federate time scheme. Supports         |

|                   | interaction between federates having different time          |

|                   | schemes.                                                     |

| Data Distribution | Supports efficient routing of data.                          |

| Management        |                                                              |

Table 1: RTI Management Areas partitioned in FedExec life cycle [8]

## CHAPTER 3

# State of the Art in the DEVS/HLA

This section briefly describes the research work in the area of the DEVS formalism and a technique used to map the DEVS model formalism onto the HLA simulation framework.

## **3.1 Implementation of the DEVS formalism**

The DEVS formalism is a well-defined means of expressing hierarchical, modular models in discrete event simulation. A DEVS model is a state machine, and the state of the model is changed by external or internal events with elapsed time. The following is a subset of the tools developed to map the DEVS formalism to simulation engines.

The *DEVS-C*++ tool is based on the DEVS formalism. It is a modular hierarchical discrete event simulation environment implemented in the object-oriented C++ language [9]. The DEVS-C++ contains three libraries: container, devs and devsHLA. The container library provides methods, which are used to organize the interacting objects (e.g. atomic models). The devs library provides methods to implement the functions as  $\delta_{ext}$ ,  $\delta_{int}$ ,  $\lambda$ , ta and port information to be defined by the user. The devsHLA library provides easy access to the DEVS/HLA environment and is discussed in section 3.2.1.

The CD++ toolkit is developed with the goal of developing and simulating models based on the DEVS and Cell-DEVS [11] paradigms. The core of the toolkit is the CD++ environment [11], which implements the DEVS and Cell-DEVS theories. The *DEVSim*++ is another tool that provides the ability to develop discrete event models using the hierarchical composition technology within the DEVS framework [12]. For simulation, DEVSim++ implements hierarchical scheduling in abstract simulators of atomic and coupled models.

## **3.2 DEVS Implementation over the HLA/RTI**

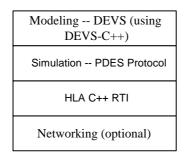

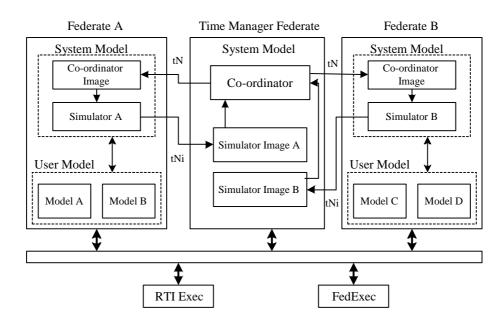

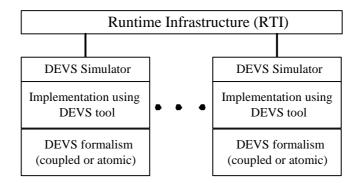

B.P.Zeigler [2] has designed and developed an HLA compliant simulation environment using DEVS as a modeling tool and a way to map the DEVS models to the HLA as shown in figure 3. The strategy underlying the mapping of the DEVS to the HLA is to exploit the information contained within the DEVS models to automate as much as possible of the programming work required for constructing the HLA compliant simulations [9]. The final goal is to facilitate a bi-directional transfer of information between the OMT Development Tool (OMDT) that captures OMT information and the DEVS model description. Figure 3 shows the layered approach and each layer is discussed in the sub-sections below.

Figure 3: Layered approach to implement the DEVS/HLA. [2]

## 3.2.1 DEVS Modeling using DEVS-C++

The top most DEVS layer of figure 3 is used for defining the models. The DEVS-C++ tool [9], as discussed in section 3.1, has a devsHLA library required for interfacing between DEVS and the HLA/RTI in a C++ environment. The devsHLA library contains methods for attribute updates, attribute reflections, interaction updates, interaction receive, object discovery and quantizers. A quantizer object is associated with each attribute that the modeler would like to publish. A quantizer is a demon that checks for the attribute value crossing the threshold. Quantizers are used to reduce message update traffic and the size of the quantizers is directly related to the accuracy and the speed of computation required.

#### **3.2.2 The Parallel DEVS (PDES) Protocol**

The Parallel and Distributed Discrete Event Simulation (PDES) protocol layer of figure 3 introduces a simulation engine, which takes care of all the time and data interactions within the DEVS models. It also acts as a message translator between the DEVS models and the HLA/RTI.

There are three approaches to mapping the DEVS formalism into the PDES protocols: Conservative, Optimistic and the Parallel DEVS. Each approach is briefly discussed below.

The *conservative scheme* [9] processes events in strict time stamped order. Conservative schemes must somehow arrange for the potential for input events with earlier time stamps to be conveyed to affected models. This can be done through "lookahead" in which each

model provides a time in the immediate future up to which it promises not to send input events. The minimum of such blackout times at any model/component, called the Lower bound time stamp (LBTS), is the time up to which it can safely process its time-stamped inputs. Thus simulation proceeds incrementally governed by the lookahead, which is the interval that a model/component adds to its current LBTS to obtain the blackout time sent to other models/components.

The *optimistic scheme* [9] permits temporary time-stamped order violation that must be repaired before the final simulation output is presented. It allows models/components to march forward in local time and process their input and output queues as fast as they can. But from time to time a model/component can receive order messages with old time-stamps. To rectify this situation, queues of already processed inputs and their outputs are maintained so that the situation can be restored to what it was just before the arrival of the old time-stamped message. This scheme has an extensive apparatus of overheads.

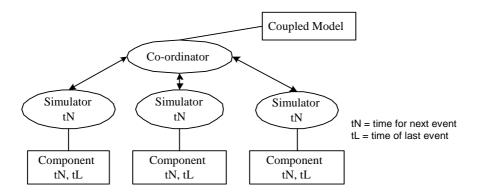

The *Parallel DEVS scheme* [9] differs from the other schemes in that there is a coordinator to synchronize the simulation cycle through its steps (see Figure 4). Unlike other schemes it does not have overheads of lookahead and local time rollbacks. In parallel DEVS, the coordinator collects all times of next events from the component simulators. It sends the minimum of these times back to the components, thereby allowing them to determine whether they are imminent (component with the least time for next event), and if so to generate output. More than one component may be imminent, and the outputs of all imminent components are sorted and distributed to others according to the coupling rules. The transition functions of the imminent components, as well as all other recipients of inputs, are then applied. Which transition is applied, depends on the

state and input of a component. The resulting changes in states may cause new values for time advances and these are sent to the coordinator. The cycle then repeats.

Figure 4: The Parallel DEVS simulation protocol [2]

## 3.2.3 Mapping of the PDES Protocol to the HLA/RTI

As shown in figure 3, B.P.Zeigler's approach to implement the PDES protocol in the HLA is as follows.

The DEVS simulation protocol is implemented with an explicit coordinator in the DEVS/HLA approach as illustrated in figure 5. Here, a separate Time Manager federate is allocated to the coordinator. This technique exploits quantizers (defined in section 3.2.1) to efficiently share the times of next events among DEVS federate and the coordinator. Only changes in local or global tN (minimum of local tNs) greater than the quantizer threshold are sent from one federate to the other using the RTI.

Figure 5: Coordinator as a Federate (the PDES protocol mapping into the HLA) [2]

## CHAPTER 4

# **Modeling Hardware Platforms**

In this chapter research motivation is discussed followed by a brief research statement and a critical analysis of the current solution to the problem as stated in chapter 3. Later, in this chapter, a solution to the research problem is proposed along with the scope of work, the contributions that are made and the presentation of the solution are discussed.

The development of systems involving computer/hardware platforms has increased tremendously. An important step during the development phase is the modeling and simulation at various levels of abstraction [10]. Simulation results play an important role in assessing the properties of the systems at various levels of abstraction.

Chapter 3 discusses a general approach to model and simulate different systems using the DEVS and the HLA/RTI. This approach can also be used in modeling and simulating computer systems and hardware platforms. A critical analysis of the technique/approach discussed in chapter 3 is as follows.

• The software tools for the DEVS implementations (section 3.1) are focused for hierarchical models (the DEVS coupled class). Hence they have complicated simulation and coordination engines in order to manage/synchronize different components. These engines perform well in the DEVS environment, but require additional message translation functionality to work with the HLA/RTI layer.

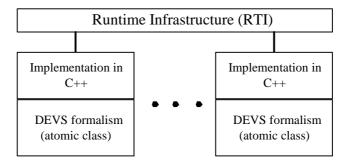

• The DEVS/HLA layered approach, discussed in section 3.2, is shown in figure 6. The two layers of simulator middleware (i.e., the RTI and the DEVS) are on top of each other. The DEVS layer is required to support the DEVS coupled models.

Figure 6: The block diagram for basic approach from chapter 3.

B.P.Zeigler's work (chapter 3) adapts the DEVS-C++ tool to the HLA/RTI structure. This is quite useful to reuse old simulations developed under the DEVS-C++ tool but suffers from the extra layer of DEVS middleware.

The motivation of this research work is to model various components of computer systems and define a simulation framework so that these components can interact with each other and give some useful results at various levels of abstractions. Another motivation is that the components could be reused in other simulations.

The research problem is to define a framework for a general hardware platform model, of a single master computer system, and to map the model onto the High Level Architecture (HLA) simulation guideline.

To address the above research problem, the DEVS formalism is used to model a hardware platform. This formalism is used, as the DEVS is an increasingly accepted paradigm for understanding and supporting the activities of modeling and simulation. In order to provide a simple solution to the research question, only the DEVS atomic class is used to model components. The rationale behind this approach is as follows.

- Atomic models can be controlled directly from the RTI, therefore an extra layer of DEVS middleware to support coupled models is not required. This approach effectively flattens the DEVS modeling hierarchy.

- Atomic models are a simple concept, and easily reusable for future developments.

The suggested layered approach to address the research problem is shown in Figure 7.

Figure 7: A Model of the proposed solution.

The scope of this research is to

• Define a simulation framework for a general hardware platform. The general hardware components to be modeled are a Processor module, a Memory module, a Bus controller module, an Interrupt module and a Timer module. Being a single master (Processor) platform, a bus arbiter is not modeled. The Processor module is further divided into three units. An Execution Unit (EU) that is responsible for decoding and executing all instructions, a Bus Interface Unit (BIU) that is responsible for performing all external bus operations and a Control Unit (CU) that is responsible for minimum/maximum mode and interrupt signals from other devices. Any required

hardware component can be modeled and added, as a future work, below the simulation (RTI) layer.

- Identify the general attributes of each hardware component in order to use these models in the initial development phase of the computer systems. The level of abstraction for these components is in the unit of bus cycles. More detailed time breakdown within a bus cycle and detailed bus level signal implementation are outside the scope of this work and may not be modeled accurately. For the execution unit (EU) of the processor the timing details are implemented up to a clock cycle.

- Use the DEVS formalism to apply the modeling and mapping results to a case study involving hardware platform components. For this case study, a Processor (a simplified version of Intel 8088), a basic Memory unit, a bus controller (a simplified version of Intel 8288), a basic Interrupt controller and a basic Timer unit are modeled.

- Execute simple operational codes as a main program and an interrupt routine on this simulator for the case study and obtain results to verify the operation of the simulator.

- Draw conclusions for the proposed solution's (discussed above) implementation in the case study.

- Summarize the contributions made by this research and the case study.

- Identify possible future research topics.

The following paragraphs identify the contributions that are made, and the approach to presenting the proposed solution.

As a contribution, a mapping of computer/hardware platforms to the HLA/RTI is developed. An approach is defined for the DEVS atomic models to work under the HLA

framework without using any additional DEVS simulators. A simulator is developed, as a case study, by modeling the hardware platform components (as discussed above in the scope of the research) using the DEVS formalism and making all the interactions between these components using the HLA framework.

In order to present the solution, the body of the thesis is organized in chapters starting from the system level discussion of hardware platform modeling using the HLA, defining the DEVS models for each hardware component, implementing the design as a case study for a simple (Intel 8088 based) platform by developing a simulator and analyzing the simulator's results to verify the proposed solution/design.

As discussed in the scope of the research, chapter 4, several modules are modeled for the platform. To reduce the amount of low-level detail only the memory module is presented in depth. For the complete implementation of all modules, appendix A.2 refers to the software code attached with the thesis. The reason for selecting the memory module, as a reference is that it is a simple module and also an important part of hardware platforms.

# CHAPTER 5

# **Simulation Framework and DEVS**

# **Atomic models**

This chapter includes the system level framework suggested to approach the solution. The discussion below starts from a system level block diagram and is later divided into two parts. In the first part the simulation flow of a Federate is described, and in the second part the DEVS atomic model for each federate is explained.

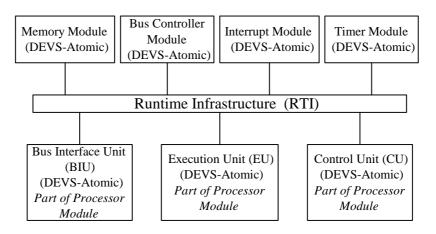

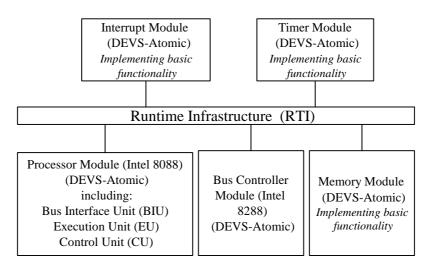

# 5.1 System Level Block diagram

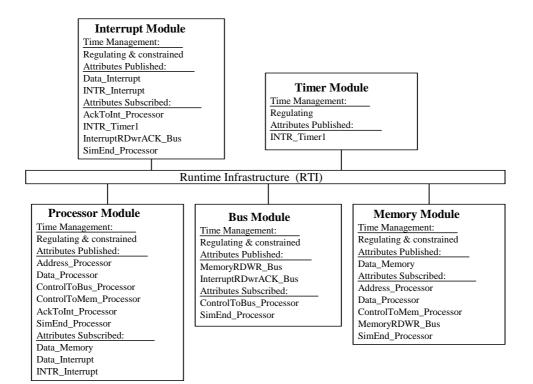

Figure 8 shows a system level block diagram for a simple hardware platform simulator. It contains the following basic hardware components: Processor module, Bus controller module, Memory module, Interrupt controller module and Timer module. The Processor module is further divided into three units: BIU, EU and CU. For modeling a single master hardware platform (chapter 4), a bus arbiter module is not required. All these components/modules are modeled using DEVS atomic models and are discussed in detail later in this chapter. In terms of the HLA, each individual component is a federate, and all federates collectively form a federation. The Runtime Infrastructure (RTI) provides the simulation platform for this federation.

Figure 8: System-level block diagram for Hardware platform simulator.

# **5.1.1 System Level Flow Diagram for a Federate**

Figure 9 shows a basic simulation flow of a federate. On the left side, the figure is labeled with numbers, which correspond to the steps in the flow chart in that row. Each step is discussed in this section by using the label references.

Figure 9: Simulation flow chart of a federate.

Step 1 is the initial step of the simulation in which a federate creates or joins a federation. If the federation does not exist, a new one is first created and then the federate is added to it. If a federation already exists, then the federate joins that federation.

At step 2, the federate is initialized. Initialization consists of the Object/Model construction, defining the attributes or/and parameters as to be published or/and

subscribed (can be re-defined during simulation), defining the federate as time regulating or/and time constrained (can be re-defined during simulation) and the registration of the federate with the federation executive. The SOM/FOM (defined in section 2.3) of each federate must also contain these published and/or subscribed attributes and/or parameters. The registration process registers the object with the federation execution, which returns an HLA object handle – an identifier for all interactions within the federation.

Step 3 allows a user to input parameters for a federate before starting the simulation loop. This step is optional, as some federates do not need any user input.

Step 4 is the first step in the simulation loop. In this step, a federate executes state transition functions according to its DEVS atomic model. The DEVS atomic models are discussed later in this chapter.

Following step 4, a federate will perform one of steps 5 or 6, depending upon its time management scheme. Step 5 is performed if a federate is time regulating (capable of sending Time Stamped Order (TSO) messages) only. The RTI grants a time advance according to the TSO message time. On the other hand if there is some incoming Receive Order (RO) message, a message with no time stamps, from another federate then the RTI delivers this message to the federate without granting a time advance. Either a time advance is granted or not, the simulation proceeds and the DEVS model transitions from one state to another.

Step 6 is performed if a federate is using either the time regulating & time constrained (capable of receiving TSO messages) both or the time constrained only scheme. The RTI grants a time advance according to the Lower Bound Time Stamp (LBTS). The LBTS is the maximum time to which a time constrained federate may advance. The LBTS is

determined by the RTI after getting the lookahead (a time period during which a federate does not send out any message) values for each federate and TSO messages from all the time regulating federates. On the other hand if there is some incoming message (either TSO or RO) from another federate then the RTI delivers this message to the federate without granting a time advance. If a time advance is granted, the federate proceeds to step 7. If a time advance is not granted, the federate returns to the top of the simulation loop for another DEVS model state transition.

At step 7, the federate checks whether the simulation loop will continue or stop. At step 8, a federate removes itself from the federation by disabling time management, resigning from the federation, deleting object instances, and, in the case where it is the last federate, destroys the federation.

## **5.1.2 DEVS Atomic Models for each Federate**

Here, DEVS atomic models for each module in Figure 8 are discussed. The memory module is discussed in detail with external/internal transition functions, time advance function and the output function. In the following sub-sections, input and output ports refer to the DEVS models as discussed in section 2.2 should not be confused with similar hardware terminology.

## **5.1.2.1 MEMORY MODULE**

The level of abstraction, as discussed in the scope of work chapter 4, can be achieved at bus cycles level. So all of the detailed signals within a bus cycle are not discussed in the model. The parameter that a user can set, as discussed in step 3 of Figure 9, is the following.

#### Parameter

Memory size (MS). This parameter has an integer value (MS > 0) and is defined in terms of bytes.

#### <u>Model</u>

Memory = < IO X S Y  $\delta_{int} \delta_{ext} \delta_{con} \lambda ta >$

#### IO - Input and output ports

- Input ports:

- Address bus: The size of address bus (AB\_Size) is an integer (AB\_Size > 0) and is defined in the processor module's parameters section 5.1.2.2. To support access to all memory locations,  $MS \le 2^{AB_Size}$ .

- Data bus: The size of the data bus (DB\_Size) is an integer (DB\_Size > 0) and is defined in the processor module's parameters section 5.1.2.2.

- Read control signal: This is a single bit signal. 1 = Read, 0 = no operation specified.

- Write control signal: This is a single bit signal. 1 = Write, 0 = no operation specified.

- Output port:

- Data bus: The size of the data bus is DB\_Size as above.

- Data acknowledge signal (for Motorola 68000 series): This is a single bit signal. 1 = Acknowledge, 0 = no operation specified.

#### <u>X – Input event set</u>

- Address on address bus: A binary value, in the range of {0,..., 2<sup>AB\_Size</sup>-1}. In order to point to a memory location, the address must be < MS.</li>

- Data on data bus: A binary value in the range of  $\{0, \dots, 2^{DB\_Size}-1\}$ .

- Read control signal  $\in \{0,1\}$ .

- Write control signal  $\in \{0,1\}$ .

#### <u>Y – Output event set</u>

- Data to data bus: A binary value as above.

- Data acknowledge signal (DTACK) informs the processor that the bus cycle has ended during an asynchronous processor's mode e.g., Motorola 68000 series processors. DTACK ∈ {0,1}.

#### <u>S – State set</u>

- Read state: In this state the memory module waits until it sends out data on the data bus acquired from the memory location as addressed by the address bus. At this level of abstraction (chapter 4), the delay function associated with this state is one bus cycle.

- Write state: In this state the memory module writes data, provided by the data bus, to a memory location which is addressed by the address bus. The module then waits until the time delay associated with this state is elapsed. At this level of abstraction (chapter 4), the delay function associated with this state is one bus cycle.

- Wait state till next  $\delta_{ext}$ . The delay function associated with this state  $\in \mathbb{R}^+$ .

#### $\delta_{ext}$ – External transition function

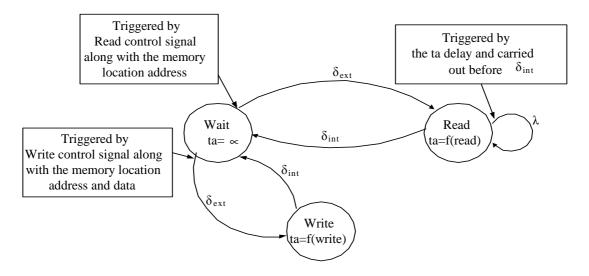

- The δ<sub>ext</sub> starts with the arrival of read/write signal on the input port of the module. In case of write signal the δ<sub>ext</sub> acquires the information from the address and data input ports. In case of read signal the δ<sub>ext</sub> only acquires the information from the address input port. As an example the state diagram for memory read and memory write during a minimum operation mode is shown in

- Figure <u>10</u>.

#### <u>ta – Time advance function</u>

- The ta function introduces the time delay before scheduling the next output function λ.

- Figure <u>10</u> shows an example where the ta function is introduced in the read state before carrying out the λ function.

#### $\lambda$ – Output function

- The λ outputs the data on the output port (data bus) during the read cycle. For the case

of Motorola 68000 series processors the DTACK signal is also sent out on the output

port. As an example see

- Figure <u>10</u>.

#### $\underline{\delta}_{int}$ – Internal transition function

- The  $\delta_{int}$  changes the internal state from read/write to the wait state. In the wait state the module stays until the next  $\delta_{ext}$ . As an example see

- Figure <u>10</u>.

#### $\delta_{con}$ – Confluent transition function

• The  $\delta_{int}$  has higher priority than the  $\delta_{ext}$

#### State Diagram for minimum operation mode

Figure  $\underline{10}$  shows a state machine diagram for the memory module. Being simpler, the minimum operation mode is used to show the transitions between different states of the module for memory read and memory write operations.

Figure 10: State diagram for memory read and write for minimum operation mode.

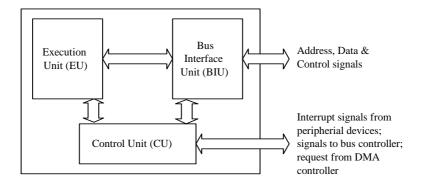

## **5.1.2.2 PROCESSOR MODULE**

A general-purpose processor module is further divided into three sub-modules. Each submodule can become a separate DEVS atomic model and communicate with the other modules using RTI services. Figure 11 shows a block diagram of the processor module.

Figure 11: Block diagram showing sub-modules in a Processor model.

#### Processor's Parameters

As discussed in step 3 of Figure 9, a user can define the following processor's parameters.

- Duration of Bus/Machine cycle (e.g.,  $8086 \approx 4$  clock cycles).

- Instruction Queue size for Bus Interface Unit (if present).

- Size of External Data (DB\_Size) and Address (AB\_Size) buses.

- External data/address buses are multiplexed or separate (for multiplexed buses external de-multiplexing circuitry is compulsory).

- Internal size of buses and registers.

- Minimum/Maximum mode (this feature is Intel specific).

- Built in cache memory if yes, cache size?

Each sub-module is modeled as follows.

#### **5.1.2.2.1 Bus Interface Unit (BIU)**

The BIU contains an instruction queue (first in first out), segment registers, instruction pointer and address/data/control buses. The main purposes of the BIU are to keep the instruction queue filled with instructions, to generate and accept the system control

signals and to act as a window between the execution unit (EU) and the memory/inputoutput (IO) devices. The DEVS atomic model for the BIU is as follows.

$$BIU = < IO \ X \ S \ Y \ \delta_{int} \ \delta_{ext} \ \delta_{con} \ \lambda \ ta >$$

#### <u>X – Input event set</u>

- Data on external data bus.

- Signal to indicate that the bus cycle has ended from the peripheral devices. This signal is required if a processor is operating in asynchronous mode e.g., Motorola 68000 series processor.

- Signals from the EU for data read/write (RD/WR) from memory or the IO devices.

- Address and Data from the EU via an internal bus.

- Signal from the EU to update instruction queue status/pointer.

- Signal from the control unit at the end of each instruction cycle indicating whether there is an interrupt request.

- In case of interrupt and jump, the execution unit shall indicate to the BIU to reset the instruction queue.

- Signal from control unit at the end of each bus cycle to indicate whether the system buses have been given under the control of DMA.

- Processor's parameters set by the user.

#### <u>Y – Output event set</u>

- Internal and external Address/data buses.

- Control signals to peripheral devices.

• Signal to control unit at the end of each bus cycle (this signal helps the control unit to act on the DMA's request).

#### $\underline{S-State \ set}$

- Opcode fetching state.

- Making physical address using code segment (CS) & instruction pointer (IP).

This is Intel specific.

- o Read data.

- o Increment IP register.

- o Increment instruction queue status/pointer.

- Data read state from the memory/IO device.

- Data write state to the memory/IO devices.

- Interrupt state.

- Wait state until the processor gets control of the system buses.

- Wait state until next external transition function.

### 5.1.2.2.2 Execution Unit (EU)

The purpose of the EU is to decode and execute the instructions that are fetched from the instruction queue. The EU contains an arithmetic and logic unit (ALU) and a register array. The ALU performs arithmetic and logic operation on memory or register data. It also contains pointer or index registers used to address operand data located in the memory. The DEVS atomic model for the EU is as follows.

$$EU = < IO X S Y \delta_{int} \delta_{ext} \delta_{con} \lambda ta >$$

#### <u>X – Input event set</u>

- Signal from the BIU:

- Arrival of an opcode in the queue.

- A signal at the completion of each request.

- Signals from the control unit:

- Interrupt request signal at the end of each instruction cycle.

- A signal at the end of each bus cycle to indicate whether the control of system buses is given over to a DMA.

- Processor's parameters set by the user.

#### <u>Y – Output event set</u>

- Signal to the BIU to execute RD/WR operation according to the decoded instruction.

- Signal to the BIU to reset the instruction queue in the case of jump and interrupt statements.

- Signal to the control unit at the end of each instruction cycle (The control unit can only respond to an interrupt request signal at the end of an instruction cycle).

### <u>S – State set</u>

- Opcode exection state. This state has following functionality.

- Read the opcode from the instruction queue.

- Decode the opcode.

- Execute the opcode. During this stage the EU has a time elapse until the BIU finishes the read or write cycle.

- Updates instruction queue pointer.

- Maintains the status of flag register.

• Wait state until next external transition function.

### 5.1.2.2.3 Control Unit (CU)

The main function of the CU is to take care of the maskable interrupt request signal, to check the non-maskable interrupt (NMI), to generate signals for the bus controller and execution unit and to check any request from the DMA/controllers to control the external bus. The DEVS atomic model for the CU is as follows.

$$CU = < IO \; X \; S \; Y \; \delta_{int} \; \delta_{ext} \; \delta_{con} \; \lambda \; ta >$$

#### <u>X – Input event set</u>

- Signal from the BIU at the end of each bus cycle.

- Signal from the EU at the end of each instruction cycle.

- Signals from peripheral devices e.g., the DMA and the interrupt controller.

- Processor's parameters set by the user.

#### Y - Output event set

- Signal to the EU for the interrupt request and DMA access to the buses.

- Signal to the BIU for the interrupt request and DMA access to the buses.

- Status signal to bus controller, prior to the initiation of bus cycle. These status signals S<sub>0</sub> S<sub>1</sub> S<sub>2</sub> are required for Intel specific maximum operation mode. These three bits are decoded by the bus controller, which then (instead of the processor) generates the appropriate control signals to the peripheral devices e.g., memory RD/WR, IO port RD/WR, interrupt acknowledge and instruction fetch signals.

#### <u>S - State set</u>

- The state of an interrupt request. (It checks the signal from the interrupt controller, the state of the instruction cycle of the processor and the status of the interrupt flag. If all the conditions are in favor of executing the interrupt routine, it generates appropriate signals to the EU and the BIU).

- The state of an external bus control request. (It checks for a signal from the DMA controller and the state of machine/bus cycle of the processor. If the conditions are satisfied it generates appropriate signals to the EU and the BIU in order to accomplish the DMA request).

- Wait state until next external transition function.

## **5.1.2.3 BUS CONTROLLER MODULE**

The bus controller module generates the control signals for the memory RD/WR from memory/input output devices, interrupt acknowledge and instruction fetch depending upon the status signal ( $S_0 S_1 S_2$ ) [14] provided by the CU of the processor module. This Intel specific bus controller module also generates some bus level control signals, which are not in the scope of this work. The DEVS model of the bus controller is as follows.

$$BC = < IO X S Y \delta_{int} \delta_{ext} \delta_{con} \lambda ta >$$

#### <u>X – Input event set</u>

• Status signals  $S_0 S_1 S_2$  from the processor module.

#### <u>Y - Output event set</u>

- Read/write control signals to the memory and input output devices.

- Interrupt acknowledge control signal.

#### <u>S – State set</u>

- Read state from the memory/input output devices.

- Write state to the memory/input output devices.

- Interrupt state. It sends out an interrupt acknowledge signal to the interrupt module.

- Wait state until next external transition function.

## **5.1.2.4 INTERRUPT CONTROLLER MODULE**

#### Function

The basic function of this module is to acquire interrupt signals from the peripheral devices connected to the input ports, prioritize these requests and send the highest priority signal to the processor. It also sends out the interrupt type number on the data lines after getting the interrupt acknowledge signal from the processor or the bus controller.

#### Model

IM =

$$<$$

IO X S Y  $\delta_{int} \delta_{ext} \delta_{con} \lambda$  ta  $>$

### X – Input event set

- Interrupt acknowledge signal from the processor and/or the bus controller.

- Interrupt from external devices.

- Input data on the external address and data buses.

- RD/WR signal from the processor and/or the bus controller.

#### <u>Y – Output event set</u>

• Interrupt request (INTR) signal or priority signals (three signals for the case of Motorola 68000 series) to the processor.

- Data out to the system data bus (to output vector type).

- Data acknowledge signal (DTACK) informs an asynchronous processor that the bus cycle has ended e.g., Motorola 68000 series processors.

#### <u>S – State set</u>

- State of initiating an interrupt request. It prioritizes the incoming interrupt signals from the peripheral devices and sends out the interrupt request or the interrupt priority code to the processor (CU).

- State of sending vector type. The interrupt controller sends out the vector type on the data bus as a result of receiving the interrupt acknowledge signal.

- Wait state till next external transition function.

## **5.1.2.5 TIMER MODULE**

This module generates a periodic signal to act as an interrupt source for the interrupt controller. As discussed in step 3 of Figure 9, a user can define the following attributes/parameters.

#### Parameters

- Duty cycle of the periodic signal.

- Number of interrupts to be generated.

#### Model

$$TM = < IO~S~Y~\delta_{int}~\delta_{ext}~\delta_{con}~\lambda~ta >$$

#### <u>Y – Output event set</u>

• Periodic signal sent to the interrupt controller.

## $\underline{S-State \ set}$

- Signal generation state.

- Wait state for time elapse. The user can set this period.

# CHAPTER 6

# **Case Study**

# **6.1 Introduction**

A hardware platform containing a processor (a simplified version of Intel 8088), a basic memory unit, a bus controller (a simplified version of Intel 8288), a basic interrupt controller and a basic timer unit is modeled using DEVS formalism. These modules interact with each other under a framework that is HLA compliant. This case study is for a synchronous platform, but no clock module is modeled. Each module assumes synchronous interactions and requests to schedule the future bus events as an integral number of clock ticks in the future.

The proposed simulation framework, as discussed in chapter 5, for hardware platform modeling using the DEVS/HLA approach is verified by the case study. This case study is done for the minimum and maximum operating modes of the processor. The user makes the selection of the operation mode (input through the keyboard) at the beginning of the execution of the processor federate as discussed in step 3 of Figure 9. For this case study, a simple simulator is developed to run the instruction codes shown in Tables 2 and 3. Later in this chapter the development of the simulator along with the hardware components' implementation are discussed.

# 6.1.1 Case study program

The example program generates 10 even numbers, from 0 to 18, and stores them in the memory module. The opcodes are shown in Table 2 along with the opcode values and the clock timing information [13]. Instruction execution times are determined by taking the number of clocks required per instruction plus any effective address (EA) time required for the operand. The EA for the indexed operand in the MOV [BX],CH instruction is 5 clocks.

| Opcode (Hex) | Program Instructions | Clock Cycle             |

|--------------|----------------------|-------------------------|

| B500         | MOV CH , 0           | 4                       |

| BF0000       | MOV DI , 0           | 4                       |

| B102         | MOV CL, 2            | 4                       |

| BB0000       | xyz : MOV BX , 00    | 4                       |

| 03DF         | ADD BX , DI          | 3                       |

| 882F         | MOV [BX] , CH        | 9 + EA = 9 + 5 = 14     |

| 47           | INC DI               | 2                       |

| 02E9         | ADD CH , CL          | 3                       |

| 83C70A       | CMP 10, DI           | 4                       |

| 750D         | JNE xyz              | 4 (when not executed)   |

|              |                      | 16 (when jump executed) |

| F4           | HLT                  | 2                       |

Table 2: Main program's opcodes for the case study

During the execution of the main program, the interrupt controller module sends interrupt signals to the processor, resulting in the execution of the interrupt routine (opcodes

shown in Table 3). The processor's interrupt behavior includes checking the interrupt flag; pushing the IP, CS and IF; sending the interrupt acknowledge to the interrupt controller; reading the vector type from the interrupt controller; calculating the starting address for the interrupt routine residing in the memory and clearing the instruction queue. The interrupt routine used in the case study increments a variable stored in memory. The opcodes for the interrupt routine along with the clock timing information are shown in Table 3 [13].

| <b>Op-code</b> (Hex) | Program Instructions | Clocks          |

|----------------------|----------------------|-----------------|

| 53                   | PUSH BX              | 15              |

| BB0020               | MOV BX , 32          | 4               |

| 8A07                 | MOV AL , [BX]        | 8+EA = 8+5 = 13 |

| FEC0                 | INC AL               | 3               |

| 8807                 | MOV [BX] , AL        | 9+EA = 9+5 = 14 |

| 5B                   | POP BX               | 12              |

| CF                   | IRET                 | 32              |

**Table 3:** Interrupt routine's opcodes for the case study

# **6.2 Simulator Implementation**

This section briefly discusses the system level block diagram for the simulator required for the case study. Later in this section each module/component is discussed in terms of the assumptions made for the implementation and flow charts for the C++ code.

## 6.2.1 System level Block diagram

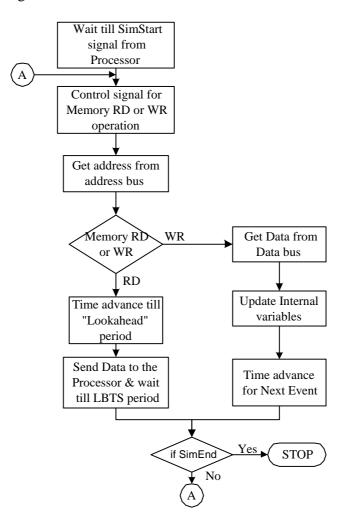

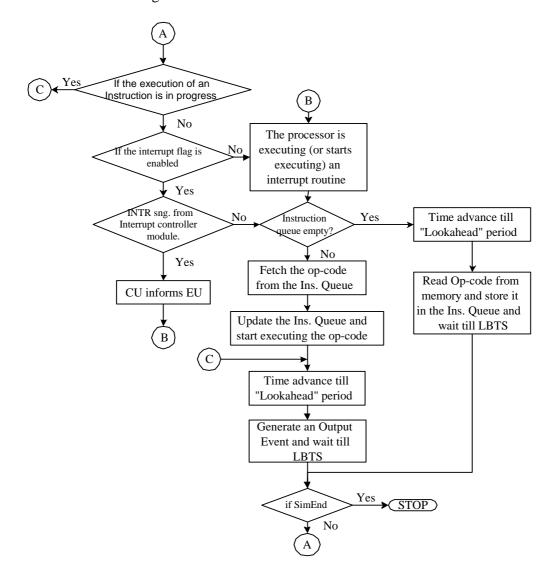

Here the Bus interface unit (BIU), execution unit (EU) and control unit (CU) are combined as a single processor module and implemented as a DEVS atomic class. A bus controller module, a basic memory module, a basic interrupt controller module and a basic timer module are implemented as defined in the scope of the research, chapter 4. The implementation details of each module are discussed later in this chapter. Figure 12 shows an overall system level block diagram implemented for the case study.

Figure 12: System level block diagram implemented for the case study.

## 6.2.1.1 Level of abstraction for the simulator's timing

For this case study one bus cycle of the processor is assumed to be four time units of the simulator. Within a bus cycle the timing details are not implemented accurately (scope of the research, chapter 4). For the execution unit of the processor the timing details are implemented with one clock cycle accuracy.

## 6.2.1.2 Algorithm to start the simulation

All federates in a federation should start the simulation simultaneously, as is the case for components in real hardware platforms. To achieve this objective, the following algorithm with two steps of signaling is defined.

The first step requires that the processor should wait until the other modules join and subscribe to the published attributes of the processor. This is achieved by executing the "enableAttributeRelevanceAdvisorySwitch()" RTI service so that the processor federate could receive the callbacks from the other federates.

The second step requires that all federates should wait for a signal from the processor federate to start the simulation. In this case study the attribute SimEnd\_Processor (see Figure 15) is the signal published by the processor module and subscribed by all the other modules. The value SimEnd\_Processor=0 indicates the starting of the simulation. The algorithm's second step addresses the scenario in which a federate has joined a federation and has no attributes to publish to a controlling federate (e.g., Processor) so the federate will not get any callbacks from the controlling federate.

## **6.2.1.3 Stopping the simulation**

If the attribute SimEnd\_Processor, as discussed in section 6.2.1.2, is set to 1 by the processor module then a signal is provided to the other modules (subscribers of the attribute) to stop the simulation.

## 6.2.1.4 Communication among Modules/Federates

Attributes are sent, from one federate to the other, in the form of AttributeHandleValuePairSet (AHVPS). AHVPS is a set comprised of attribute handles, values and the size of the values. To create the AHVPS, a method CreateNVPSet(), extracted from the memory module's software code, is defined in Figure 13. In this example the RTI method "AttributeSetFactory::create(1)" creates the AHVPS for only one AHVP, as there is only one attribute to send out i.e., "DataFromMem". The following example also shows that the AHVPS is only created if the attribute "DataFromMem" is changed. Section 6.2.2.2.1 further explains how this AHVPS is received and the attributes are extracted by a federate.

```

// Setting up the data structure required to send this object's state to the RTI.

RTI::AttributeHandleValuePairSet* Memory::CreateNVPSet()

```

```

RTI::AttributeHandleValuePairSet* pMemoryAttributes = NULL;

// Make sure the RTI Ambassador is set.

if (ms_rtiAmb)

{

//----

// Set up the data structure required to send this object's state to the RTI.

//----

pMemoryAttributes = RTI::AttributeSetFactory::create(1);

if ( hasDataFromMemChanged == RTI::RTI_TRUE )

{

pMemoryAttributes -> add( this -> GetDataFromMemRtiId(),(char*) &this -> GetDataFromMem(),

(sizeof(int)));

out2file << "Data From Memory = " << DataFromMem << endl;

}

}

return pMemoryAttributes;

}

```

Figure 13: Creating an AHVPS for communication among Module/Federates.

## 6.2.1.5 Time elapse using RTI

The software code, in Figure 14, shows that the module has sent a time elapse request to the RTI according to the time calculated (represented by the "requestTime") for the next event. The lookahead value (see step 6 Figure 9) is set to 0.5, means that the federate will not send any output until this period is elapsed. The time step value is set to 1.0, means that this is the maximum limit for the time elapse requested to the RTI. The final "requestTime" is calculated by adding the time step value of 1.0 and the "grantTime", which is the time granted in the previous time elapse request. In other words the "grantTime" is the current simulation time. The RTI method "nextEventRequest(requestTime)" requests for the time elapse until the "requestTime". In return, the RTI grants the time advance until the next event. The tick() function gives control to the RTI for processing the ongoing events/tasks.

## 6.2.1.6 Logging simulator activity

The logging capability is developed for all the modules of the simulator. Each module has its own logging file. Whenever a module receives or updates an attribute it sends this information to a file to maintain the logs. The status of the internal registers (e.g., processor module) and the memory dumps are also stored in the file. All this information is logged with the simulator's time stamp. These logs are explained in chapter 7 and the message flow and timing information is extracted and analyzed. The "out2file" statement in Figure 14 is sending data to a log file.

## 6.2.1.7 FOM/SOM

This section identifies the time management parameters and the interaction attributes used by each federate. This information is a part of a FED file (discussed in section 2.3) that provides an interface between the DEVS model and the RTI layer. Figure 15 shows the names of the attributes used in this case study. These attributes are the input output ports of the DEVS model of each component in the case study. As an example take the memory and the processor modules/federates. The processor's relevant published attributes (e.g., Address\_Processor) are included in the subscribed attributes of the memory federate and vice versa.

Figure 15: Block diagram containing time management and attribute information.

## 6.2.2 Memory Module

In this section the assumptions made for the memory module, development of the module using the DEVS formalism along with the excerpts from the software code and the software flow chart are discussed.

## 6.2.2.1 Assumptions

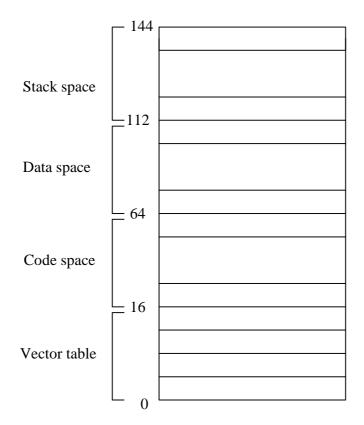

The Memory size is assumed to be 144 Bytes as it fulfils the requirement of the case study. It is assumed that this memory module does not introduce wait states. The processor has divided the memory module into logical segments as shown in Figure 16. Each number in this figure is a decimal value. An Extra segment is not implemented, as there is no string operation involved in this case study.

Figure 16: Memory map for 8-bit structure (specific to the case study)

## 6.2.2.2 Development of Memory module

This section discusses the implementation of the memory module on the basis of the DEVS formalism. It explains the software development of the module's external transition function, duration function, output function, internal transition function and confluent transition function. For further details, the complete software code of this module along with the whole simulator is referred in Appendix A.2.

## 6.2.2.2.1 External transition function ( $\delta_{ext}$ )

During the  $\delta_{ext}$  function, the control signal (read/write) from the processor or bus controller module arrives along with the address on the address bus. If the control signal

is for a memory write operation, the data on the data bus is also required from the processor. The software implementation of the  $\delta_{ext}$  function is implemented as shown in Figure 17. The figure is further divided into sections to facilitate discussion.

As an example, following is a detailed discussion of the memory read operation. To initiate the memory read cycle, the federate ambassador is informed through the RTI that the "ControlSignalFromProToMem" and the "AddressFromPro" attributes have arrived through the input ports of the memory module (as discussed in section 6.2.1.6), each in the form of AHVPS. In order to update the attributes of the memory module, the federate ambassador then calls the "Update(const RTI::AttributeHandleValuePairSet&)" method, shown in Figure 17, section A. Due to the two incoming attributes, the value returned by the "theAttributes.size()" equals to 2 and the "for" loop is executed twice. The actual values of the incoming attributes are extracted and saved using the getHandle() and getValue() methods. The "Out2file" saves these attributes to a log file. The value of the "ControlSignalFromProToMem" attribute tells whether this is a memory read or memory write operation. Assuming this value is for a memory read operation, the "DataFromMem" variable is updated as shown in Figure 17, section B. A flag "hasDataFromMemChanged" is also set so that when UpdateFromMem(FederateTime) method (Figure 17, section D) is called this updated value is sent out to the RTI. Figure 17, section D shows that the state of the memory is updated in terms of time and the new AHVPS are created for the variables that are changed (e.g., "DataFromMem"). CreateNVPSet() method creates the AHVPS as discussed in section 6.2.1.4. These AHVPS are sent out to the RTI during the output function as discussed in section 6.2.2.3.

```

----- SECTION A -----

void Memory::Update( const RTI::AttributeHandleValuePairSet& theAttributes )

RTI::AttributeHandle attrHandle;

RTI::Ulong

valueLength;

// We need to iterate through the AttributeHandleValuePairSet to extract each AttributeHandleValuePair.

// Based on the type specified ( the value returned by getHandle() ) we need to extract the data from the

// buffer that is returned by getValue().

for (unsigned int i = 0; i < theAttributes.size(); i++)

ł

attrHandle = theAttributes.getHandle( i );